This is an electronic reprint of the original article. This reprint may differ from the original in pagination and typographic detail.

Marangalu, Milad Ghavipanjeh; Kurdkandi, Naser Vosoughi; Alavi, Peyman; Khadem, Saeideh; Tarzamni, Hadi; Mehrizi-Sani, Ali A New Single DC Source Five-Level Boost Inverter Applicable to Grid-Tied Systems

Published in: IEEE Access

DOI: 10.1109/ACCESS.2023.3253806

Published: 01/01/2023

Document Version Publisher's PDF, also known as Version of record

Published under the following license: CC BY

Please cite the original version: Marangalu, M. G., Kurdkandi, N. V., Alavi, P., Khadem, S., Tarzamni, H., & Mehrizi-Sani, A. (2023). A New Single DC Source Five-Level Boost Inverter Applicable to Grid-Tied Systems. *IEEE Access*, *11*, 24112-24127. https://doi.org/10.1109/ACCESS.2023.3253806

This material is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

Received 17 February 2023, accepted 4 March 2023, date of publication 8 March 2023, date of current version 14 March 2023.

Digital Object Identifier 10.1109/ACCESS.2023.3253806

# **RESEARCH ARTICLE**

# **A New Single DC Source Five-Level Boost Inverter Applicable to Grid-Tied Systems**

MILAD GHAVIPANJEH MARANGALU<sup>D1</sup>, NASER VOSOUGHI KURDKANDI<sup>D2</sup>, (Member, IEEE), PEYMAN ALAVI<sup>®3</sup>, SAEIDEH KHADEM<sup>®4</sup>, (Member, IEEE),

HADI TARZAMNI<sup>©5</sup>, (Student Member, IEEE), AND

ALI MEHRIZI-SANI<sup>®6</sup>, (Senior Member, IEEE) <sup>1</sup>Faculty of Electrical and Computer Engineering, University of Tabriz, Tabriz 51666-16471, Iran

<sup>2</sup>Department of Electrical and Computer Engineering, San Diego State University, San Diego, CA 92182, USA

<sup>3</sup>School of Electrical Engineering and Computer Science, Penn State University, State College, PA 16801, USA

<sup>4</sup>Program of Electrical Engineering and Industrial Applied Mathematics, California State University Long Beach, Long Beach, CA 90840, USA

<sup>5</sup>Department of Electrical Engineering and Automation, Aalto University, 02150 Espoo, Finland <sup>6</sup>Bradley Department of Electrical and Computer Engineering, Virginia Tech, Blacksburg, VA 24061, USA

Corresponding author: Hadi Tarzamni (hadi.tarzamni@aalto.fi)

This work was supported by Finnish Electronic Library (FinElib), Finland, under the FinELib Consortium's Agreement with IEEE.

**ABSTRACT** In this paper, a single source five-level boost inverter has been proposed and analyzed. The proposed structure includes a five-level inverter and a single-input multi-output (SIMO) boost converter. In this structure, the DC link voltage has been controlled by controlling the implemented DC-DC boost converter. In addition, the inverter switching pattern has been obtained based on the pick current control (PCC) method. In order to test and prove the performance of the proposed structure, this system is tested with the local grid. Since the active and reactive powers have been controlled based on the PCC method, the generated energy in a renewable energy source can be transferred to the local grid with a controlled and high-quality current. In this paper, the proposed structure has been introduced and its operation in different modes has been analyzed completely. Furthermore, the design considerations of the required elements have been investigated. Also, the power loss analysis and the comparison results of the proposed converter with other similar structures have been presented. Finally, in order to test the practical performance of the proposed structure and prove the theoretical analysis, a 620 W laboratory prototype of this structure has been assembled and its performance with the local grid has been tested.

**INDEX TERMS** Multilevel inverter, DC–DC converter, peak current control (PCC).

#### I. INTRODUCTION

The multilevel inverters have been extensively studied in recent years and still are interesting for both academics and engineers. In the last ten years, research works have been concentrated on exploring new topologies for multilevel inverters. Therefore, a huge number of multilevel inverters with reduced circuit components have been presented in the literature. In these structures, the main purpose is reducing the number of the required power switches [1], [2], [3], [4] and DC voltage sources [5], [6], [7], [8], [9], [10]. In order

The associate editor coordinating the review of this manuscript and approving it for publication was Chi-Seng Lam

to provide higher number of output voltage levels (high resolution), the presented inverters with reduced number of components contain considerably lower number of components in comparison with conventional inverters. However, in practical applications, the output voltage with considerable high voltage levels may not be required. On the other hand, almost in all the multilevel inverters with reduced number of components, some interesting features of the conventional multilevel inverters such as modularity may be lost. To provide high resolution with considerable number of voltage levels, this condition is even more intensified. Therefore, implementing multilevel inverters with high voltage levels may not be efficient practically.

Although voltage boosting capability of the multilevel inverters is an interesting and useful feature for these inverters, this topic has not been investigated as widely as the component reduction topic. The presented topologies in [11], [12], [13], [14], [15], and [16] benefit from voltage boosting capability. In [11], a multilevel inverter with switched-battery based voltage bosting capability has been presented. In this topology, the implemented batteries get charge from the DC source and their series connections boost the inverter input voltage. Since more switching elements have been required to derive the mentioned switched-battery system, this structure suffers from high number of the switching elements. In [12], a thirteen-level inverter with voltage boosting capability has been introduced. In this inverter, the voltage boosting capability has been obtained based on the capacitors partial charging method. In order to obtain the expected voltage levels, the capacitors should be charged in different voltage levels. Consequently, this partial charging results in high total harmonic distortion (THD) of the output voltage. In [13], in order to achieve the voltage boosting capability, a Z-network has been added to the conventional cascaded H-bridge (CHB) multilevel inverter. In this structure, in order to implement only one Z-network for all the utilized H bridges, the utilized H-bridges are cascaded via low-frequency (LF) transformers which results in the overall system's high cost. The presented topology in [14] is a five-level inverter with eight power switches, two LF transformers, and a Z-network. In this structure, the voltage boosting capability has been provided by the separate DC-DC boost converter of each bridge. Since each bridge requires its DC source and DC-DC boost converter, this method cannot be efficient. Also, in order to modify the output voltage quality in lower output conditions, the idea of regulating the multilevel inverters DC voltage in response of changing the required output voltage magnitude has been presented in [15] and [16].

The presented five-level inverters in [17], [18], [19], and [20] require more than one DC source to provide the expected output voltages. However, the presented five-level inverters in [21], [22], [23], and [24] are capable of providing the expected output voltages with only one DC source. The introduced single source five-level inverters in [24] and [25] contain twelve and five power switches, respectively. Voltage boosting capability cannot be achieved by these structures. In [26], a new single DC source five-level inverter based on the fault tolerant method has been presented. This topology contains eight power switches and two power diodes. Similar to [24] and [25], the voltage boosting capability cannot be obtained by this topology.

In this paper, a single source multilevel inverter with boosting capability and lower number of components has been proposed. In this topology, the implemented converter in DC side has been analyzed and controlled based on the inverter's output voltage. Therefore, it is possible to improve the quality of the inverter's output voltage by regulating the DC sides voltages. Also, the PCC control method has been implemented to generate the inverter's switching pulses and regulate the

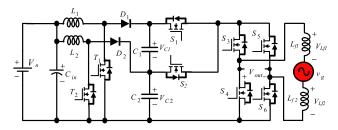

FIGURE 1. Proposed five-level boost inverter.

TABLE 1. Switching table of the proposed five-level inverter.

| $\mathbf{S}_1$ | $S_2$ | <b>S</b> <sub>3</sub> | <b>S</b> 4 | <b>S</b> 5 | <b>S</b> <sub>6</sub> | Switch<br>Voltage |

|----------------|-------|-----------------------|------------|------------|-----------------------|-------------------|

| 1              | 0     | 1                     | 0          | 0          | 1                     | $V_{dc}$          |

| 0              | 1     | 1                     | 0          | 0          | 1                     | $V_{dc}/2$        |

| 0              | 0     | 1                     | 0          | 1          | 0                     | 0                 |

| 0              | 1     | 0                     | 1          | 1          | 0                     | $-V_{dc}/2$       |

| 1              | 0     | 0                     | 1          | 1          | 0                     | $-V_{dc}$         |

active and reactive powers. In order to prove the performance of the proposed topology, a laboratory prototype of the introduced setup has been tested with the local grid and the results have been investigated. In this paper, the proposed topology, the operational modes of the introduced five-level inverter, control method of the implemented DC-DC converter, and control method of the proposed inverter have been presented in section II. The design of the implemented elements has been discussed in section III. In section IV, the power loss analysis of the proposed structure has been investigated. Also, a comparison study between the proposed five-level inverter and other related topologies has been presented in section V. In order to verify the dynamic response of the proposed inverter, some simulation results are provided in Section VI. Finally, in order to test the performance of the proposed setup and verify the claimed advantages of this structure, a 620 W laboratory prototype of the introduced structure has been assembled and the results have been investigated in section VII.

# II. PROPOSED TOPOLOGY AND IMPLEMENTED CONTROL SYSTEMS

In this section, the completely description of the proposed topology and its operation modes are presented. Also, the implemented control systems of the proposed inverter are provided.

#### A. PROPOSED TOPOLOGY

The schematic of the proposed topology has been illustrated in Fig. 1. This structure is a modified version of the presented inverter in [27]. Based on Fig. 1, the proposed structure is a combination of a SIMO DC-DC boost converter and a multilevel inverter. Since the inverter side is a five-level inverter, in the DC side, a single-input two-output DC-DC converter is required. The implemented five-level inverter is a six-switch inverter and this inverter is connected to the two

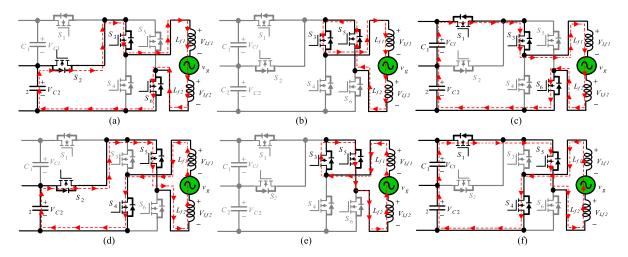

FIGURE 2. Operational modes of the proposed five-level inverter a) Mode 1, b) Mode 2, c) Mode 3, d) Mode 4, e) Mode 5, f) Mode 6.

output capacitors of the DC side. In Fig. 1, the implemented DC-DC converter contains two MOSFETs ( $T_1$  and  $T_2$ ), two inductors  $(L_1 \text{ and } L_2)$ , two power diodes  $(D_1 \text{ and } D_2)$ , and two output capacitors ( $C_1$  and  $C_2$ ). In this structure, two DC side output capacitors are the connection link between the DC side and inverter side. By controlling the implemented DC-DC converter, both the DC side output voltages ( $V_{C1}$  and  $V_{C2}$ ) can be controlled autonomously. Therefore, by implementing a DC voltage source ( $V_{in} = V_{dc}$ ), two non-isolated DC voltage sources have been obtained in the output of DC side. Since, autonomous control of the output DC voltages is possible, even with unequal power delivery from the output capacitors, the proposed structure can provide the desired performance. In fact, in the proposed structure, during a common cycle, the output capacitor  $C_2$  transfers more power than output capacitor  $C_1$ . As a result, the mentioned feature is vital for the performance of the proposed structure. In Fig. 1, the implemented five-level inverter contains six power switches  $(S_1$ - $S_6)$ . The power switches  $S_1$  and  $S_2$  have been implemented to generate the output voltage levels. Also, the H-bridge part (switches  $S_3$ - $S_6$ ) has the responsibility of changing the voltage polarity to obtain the desired AC voltage in the output side of the inverter. Furthermore, the H-bridge switches  $(S_3-S_6)$  generate the zero-voltage level of the output voltage waveform. The switching states of the proposed inverter have been presented in Table 1. This pattern is obtained based on the pick current control (PCC) method. The detailed information about this method and obtaining the switching pattern has been presented in the control strategy subsection. In order to provide a five-level voltage waveform with equal steps, the voltages of the output capacitors  $(V_{C1} \text{ and } V_{C2})$  should be equal. In the proposed inverter, the DC link voltage ( $V_{DC,link} = V_{C1} + V_{C2}$ ) can be regulated based on the required output voltage. Based on the switching pattern, the proposed inverter has six different operational modes and the equivalent circuits of these modes have been illustrated in Fig. 2.

# B. PROPOSED FIVE-LEVEL INVERTER OPERATIONAL MODES

### 1) FIRST OPERATIONAL MODE

The equivalent circuit of the proposed inverter in the first operational mode has been shown in Fig. 2(a). In this mode, the power switches  $S_2$ ,  $S_3$ , and  $S_6$  are in on state. Therefore, the stored energy in the capacitor  $C_2$  transfers to the output side and the current of the output inductor increases linearly. Also, due to off state of the power switch  $S_1$ , the capacitor  $C_1$  does not conduct. As a result, the magnitude of the output voltage is equal to the voltage of the capacitor  $C_2$  ( $V_{out} = +V_{dc}/2$ ).

In this mode, the power switches voltage stresses can be obtained as follows:

$$V_{S1} = V_{C1} = V_{dc}/2 \tag{1}$$

$$V_{S4} = V_{S5} = V_{C2} = V_{dc}/2 \tag{2}$$

#### 2) SECOND OPERATIONAL MODE

The equivalent circuit of the second operational mode is shown in Fig. 2(b). In this mode, the power switches  $S_3$  and  $S_5$  are in on state. Therefore, the output current is reduced and the zero-voltage level has been generated in the output voltage waveform.

#### 3) THIRD OPERATIONAL MODE

Fig. 2(c) illustrates the equivalent circuit of the proposed structure in the third operational mode. In this mode, the power switches  $S_1$ ,  $S_3$ , and  $S_6$  are in on state. Furthermore, the capacitors  $C_1$  and  $C_2$  transfer energy to the output side simultaneously. As a result, the output voltage magnitude is equal to the DC link voltage ( $V_{out} = +V_{dc}$ ).

The power switches voltage stresses can be achieved as follows:

$$V_{S2} = V_{C1} = V_{dc}/2$$

(3)

$$V_{S4} = V_{S5} = V_{C1} + V_{C2} = V_{dc} \tag{4}$$

#### 4) FORTH OPERATIONAL MODE

Fig. 4(d) shows the proposed inverter in the fourth operational mode. In this mode, the switches  $S_2$ ,  $S_4$ , and  $S_5$  are in on state. Consequently, the first negative voltage level in the negative half cycle has been generated and the output voltage is equal to  $-V_{dc}/2(V_{out} = -V_{dc}/2)$ . In this mode, the direction of the output current has been changed.

In this mode, the power switches voltage stresses can be obtained as follows:

$$V_{S1} = V_{C1} = V_{dc} / 2 \tag{5}$$

$$V_{S3} = V_{S6} = V_{C2} = V_{dc} / 2 \tag{6}$$

#### 5) FIFTH OPERATIONAL MODE

Fig. 2(e) shows the proposed inverter in the fifth operational mode. Based on this figure, the power switches  $S_3$  and  $S_5$  are in on state. As a result, the zero voltage level of the output voltage has been generated in the negative half cycle.

#### 6) SIXTH OPERATION MODE

Fig. 2(f) illustrates the equivalent circuit of the proposed inverter in the sixth operational mode. In this mode, the switches  $S_1$ ,  $S_4$ , and  $S_5$  are in on state. The output voltage is negative and the second voltage level of the negative half cycle has been generated. Therefore, the output voltage is equal to  $-V_{dc}$  ( $V_{out} = -V_{dc}$ ).

The power switches voltage stresses can be obtained as follows:

$$V_{S2} = V_{C1} = V_{dc} / 2 \tag{7}$$

$$V_{S3} = V_{S6} = V_{C1} + V_{C2} = V_{dc} \tag{8}$$

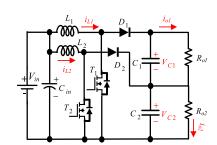

# C. DYNAMIC MODEL AND CONTROL METHOD OF THE IMPLEMENTED SIMO DC-DC CONVERTER

As discussed, a SIMO DC/DC converter has been implemented to provide two equal output voltages ( $V_{C1}$  and  $V_{C2}$ ) from a single input DC voltage ( $V_{in}$ ). The schematic of the implemented DC-DC converter without adding the proposed five-level inverter has been illustrated in Fig. 3. In order to control the output voltages ( $V_{C1}$  and  $V_{C2}$ ) based on the switch's duty cycles ( $d_1$  and  $d_2$ ), the dynamic model of the implemented DC-DC converter can be described as follows:

$$\dot{x} = Ax + Bu, \quad y = Cx + Du \tag{9}$$

where x is the state space matrix, u is the input vector matrix, and y is the output vector matrix. In the implemented DC-DC converter, there are four energy storage elements  $(L_1, L_2, C_1, \text{ and } C_2)$ . Therefore, state space matrix, input and output matrixes can be described as follows:

$$x^{T} = \begin{bmatrix} i_{L1} & i_{L2} & v_{C1} & v_{C2} \end{bmatrix}, u^{T} = [v_{in}], y^{T} = [v_{C1} & v_{C2}]$$

(10)

Analyzing the implemented DC-DC converter, the state space variables can be obtained as follows:

$$\frac{di_{L1}}{dt} = \frac{V_{in}}{L_1} + \frac{V_{C1} + V_{C2}}{L_1} (d_1 - 1)$$

(11)

$$\frac{di_{L2}}{dt} = \frac{V_{in}}{L_2} + \frac{V_{C2}}{L_2} (d_2 - 1)$$

(12)

$$\frac{dV_{C1}}{dt} = \frac{i_{L1}}{C_1} \left(1 - d_1\right) - \frac{V_{C1}}{R_{o1}C_1}$$

(13)

$$\frac{dV_{C2}}{dt} = \frac{i_{L1}}{C_2} \left(1 - d_1\right) + \frac{i_{L2}}{C_2} \left(1 - d_2\right) - \frac{V_{C2}}{R_{o2}C_2}$$

(14)

Based on small signal model, all the variables contain a DC part  $(\bar{X}, \bar{Y}, \bar{U}, \bar{D})$  and an AC part  $(\tilde{x}, \tilde{y}, \tilde{u}, \tilde{d})$ . As a result, this equation can be written:

$$x = \bar{X} + \tilde{x}, \ y = \bar{Y} + \tilde{y}, \ u = \bar{U} + \tilde{u}, \ d_{1,2} = D_{\bar{1},2} + \tilde{d}_{1,2}$$

(15)

In this converter, the purpose is controlling the output voltages ( $V_{C1}$  and  $V_{C2}$ ) by regulating the duty cycles ( $d_1$  and  $d_2$ ). Therefore, considering that the AC values are almost constant during a switching period and are noticeably smaller than DC values ( $\bar{X} \gg \tilde{x}, \bar{Y} \gg \tilde{y}, \bar{U} \gg \tilde{u}, \bar{D} \gg \tilde{d}$ ), the small signal model of this converter can be rewritten as follows:

$$\widetilde{x} = A'\widetilde{x} + B'\widetilde{u}, \ \widetilde{y} = C'\widetilde{x}$$

(16)

where  $\tilde{x}$ ,  $\tilde{u}$ , and  $\tilde{y}$  can be described as follows:

$$\widetilde{x}^{T} = \begin{bmatrix} \widetilde{i}_{L1} & \widetilde{i}_{L2} & \widetilde{v}_{C1} & \widetilde{v}_{C2} \end{bmatrix}, \\

\widetilde{u}^{T} = \begin{bmatrix} \widetilde{d}_{1} & \widetilde{d}_{2} \end{bmatrix}, \quad \widetilde{y}^{T} = \begin{bmatrix} \widetilde{v}_{Co1} & \widetilde{v}_{Co2} \end{bmatrix}$$

(17)

Now, considering (11-17), matrixes  $A'(n \times n)$ ,  $B'(n \times n)$ , and  $C'(m \times n)$  can be obtained as follows:

$$A' = \begin{bmatrix} 0 & 0 & \frac{(\bar{D}_1 - 1)}{L_1} & \frac{(\bar{D}_1 - 1)}{L_1} \\ 0 & 0 & 0 & \frac{(\bar{D}_2 - 1)}{L_2} \\ \frac{(1 - \bar{D}_1)}{C_1} & 0 & -\frac{1}{R_{o1}C_1} & 0 \\ \frac{(1 - \bar{D}_1)}{C_2} & \frac{(1 - \bar{D}_2)}{C_2} & 0 & -\frac{1}{R_{o2}C_2} \end{bmatrix}$$

(18)

$$B' = \begin{bmatrix} \frac{\bar{V}_{C1} + \bar{V}_{C2}}{L_1} & 0 & \frac{-\bar{I}_{L1}}{C_1} & \frac{-\bar{I}_{L1}}{C_2} \\ 0 & \frac{\bar{V}_{C2}}{L_2} & 0 & \frac{-\bar{I}_{L2}}{C_2} \end{bmatrix}^T$$

(19)

$$C' = \begin{bmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

(20)

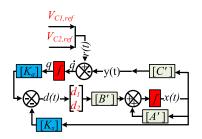

The schematic of the implemented pole placement control method [28] has been illustrated in Fig. 4. Considering, this figure, these equations can be written:

$$\begin{array}{ll} u = -K_x \tilde{x} - K_q q & (21) \\ q = r - y = r - C' \tilde{x} & (22) \end{array}$$

where q and r are the integrator's output and the reference signals of the output variables.

$$r(t)^{T} = \begin{bmatrix} V_{C1,ref} & V_{C2,ref} \end{bmatrix}$$

(23)

Considering (22), these equations can be obtained:

$$q_1^{\cdot}(t) = V_{C1,ref} - V_{C1}, \quad q_2^{\cdot}(t) = V_{C2,ref} - V_{C2}$$

(24)

Implementing the described control method in a complete state controllable system, it is possible to shift the poles of the system to the desired locations by regulating the control matrixes [28], [29]. The controllability matrix can be defined as follows:

$$\Phi_{c} = \begin{bmatrix} B' | A'B' | A'^{2}B' | \dots | A'^{n-1}B' \end{bmatrix}$$

$$= \begin{bmatrix} B' | A'B' | A'^{2}B' | A'^{3}B' \end{bmatrix}$$

(25)

Now, the complete rank of the controllability matrix can guarantee the system's complete controllability. Therefore, the following condition should be fulfilled:

$$rank(\Phi_c) = n = 4 \tag{26}$$

Considering (16) and (22), the open-loop matrixes can be written as follows:

$$\begin{cases} \begin{bmatrix} \dot{\tilde{x}}(t) \\ q(t) \end{bmatrix} = \begin{bmatrix} A' & 0 \\ -C' & 0 \end{bmatrix} \begin{bmatrix} \tilde{x}(t) \\ q(t) \end{bmatrix} + \begin{bmatrix} B' \\ 0 \end{bmatrix} \tilde{u}(t) \\ + \begin{bmatrix} 0 \\ I \end{bmatrix} r(t) \qquad (27) \\ y(t) = \begin{bmatrix} C' & 0 \end{bmatrix} \begin{bmatrix} \tilde{x}(t) \\ q(t) \end{bmatrix} \\ \hat{A}' = \begin{bmatrix} A' & 0 \\ -C' & 0 \end{bmatrix}, \quad \hat{B}' = \begin{bmatrix} B' \\ 0 \end{bmatrix} \qquad (28)$$

Now, the new controllability matrix can be achieved as follows:

$$\overline{\Phi_c} = \left[ \hat{B}' \middle| \hat{A}' \hat{B}' \middle| \hat{A}'^2 \hat{B}' \middle| \dots \middle| \hat{A}'^{n-1} \hat{B}' \right]$$

$$= \left[ \hat{B}' \middle| \hat{A}' \hat{B}' \middle| \hat{A}'^2 \hat{B}' \middle| \hat{A}'^3 \hat{B}' \right]$$

$$= \left[ \begin{array}{c} B' \middle| A'B' \middle| A'^2 B' \middle| \hat{A}'^3 \hat{B}' \\ 0 \middle| -C' \middle| -C' A'B' \middle| -C' A'^3 B' \end{array} \right]$$

(29)

$$\overline{\Phi_c} = \underbrace{\begin{bmatrix} B' & A' \\ 0 & q - C' \end{bmatrix}}_{M} \begin{bmatrix} I & 0 \\ 0 & \Phi_c \end{bmatrix}$$

(30)

Now, the system is complete controllable when rank(M) is equal to n + m:

$$rank(M) = n + m = 6 \tag{31}$$

Considering parameter values from Table 2, Six eigenvalues of  $\hat{A}'$  have been achieved as follows:

$$e_{1,2} = 0, \quad e_{3,4} = -5.4 \pm 977.2i, \quad e_{5,6} = -7.9 \pm 2558.3i$$

(32)

All the eigenvalues should be completely shifted to the left side of the Jw axis. New desired locations for eigenvalues can be written as follows:

$$e'_{1,2} = -45500, \ e'_{3,4} = -5005 \pm 977.2i,$$

$e'_{5,6} = -1258 \pm 2558.3i$  (33)

FIGURE 3. Schematic of the implemented DC-DC converter.

TABLE 2. Implemented components in the DC side .

| Parameter    | Туре             | Explanation   |  |  |

|--------------|------------------|---------------|--|--|

| $V_{in}$     | Fixed DC Voltage | 100V          |  |  |

| $V_{CI}$     | Fixed DC Voltage | 200V          |  |  |

| $V_{C2}$     | Fixed DC Voltage | 200V          |  |  |

| $C_1 \& C_2$ | Electrolytic     | 1000µF-250 V  |  |  |

| $L_1 \& L_2$ | Ferrite Core     | $100 \ \mu H$ |  |  |

Using the formula in MATLAB, to shift the eigenvalues to their new locations in the closed loop system, the control matrixes  $K_x$  and  $K_q$  can be obtained as follows:

$$K = [K_x, K_q] = \operatorname{place}(\hat{A}', \hat{B}', e')$$

(34)

$$K_{x} = \begin{bmatrix} 0.0134 & 0.00040.14280.0176 \\ -0.0011 & 0.0257 & -0.2264 & 0.1299 \end{bmatrix}$$

(35)

$$K_q = \begin{bmatrix} -117.2982 & -129.1656\\ 697.7264 & -164.3719 \end{bmatrix}$$

(36)

Since the designed control method is type one, it is capable of tracking the input reference values without steady-state error.

Now, combining (22) and (27), the new system can be described as follows:

$$\begin{cases} \begin{bmatrix} \dot{\tilde{x}}(t) \\ \dot{q}(t) \end{bmatrix} = \begin{bmatrix} A' - B'K_x & -B'K_q \\ -C' & q0 \end{bmatrix} \begin{bmatrix} \tilde{x}(t) \\ q(t) \end{bmatrix} + \begin{bmatrix} 0 \\ I \end{bmatrix} r(t)$$

$$y(t) = \begin{bmatrix} C' & 0 \end{bmatrix} \begin{bmatrix} \tilde{x}(t) \\ q(t) \end{bmatrix}$$

(37)

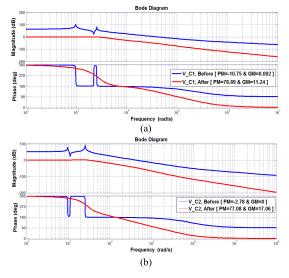

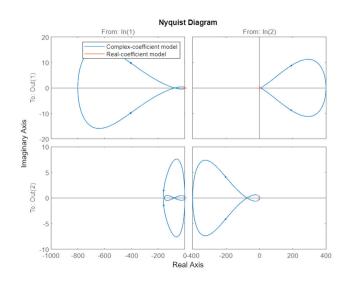

Fig. 5 illustrates the bode diagrams of the implemented DC-DC converter. In this figure, the bode diagrams of the both output voltages ( $V_{C1}$  and  $V_{C2}$ ) have been shown before and after implementing the described control method. Based on these bode diagrams, the gain margin (GM) values have been regulated to 11.24 and 17.06 for  $V_{C1}$  and  $V_{C2}$ , respectively. In addition, the values of the phase margin (PM) have been regulated to 78.89 and 77.08 for  $V_{C1}$  and  $V_{C2}$ , respectively. Therefore, both the GM and PM values are in the desired range (GM>10 and 60<PM<80) and the output voltages have been controlled based on duty cycles properly. Furthermore, in order to provide additional analysis of the control system, the Nyquist diagram of the implemented control method has been illustrated in Fig. 6.

**FIGURE 4.** Schematic of the implemented control method of DC-DC converter.

**FIGURE 5.** Bode diagrams before and after implementing control method (a) for  $V_{C1}$  (b) for  $V_{C2}$ .

FIGURE 6. The Nyquist diagram of the implementing control method.

# D. CONTROL STRATEGY OF THE PROPOSED FIVE-LEVEL BOOST INVERTER

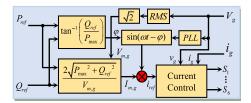

In order to analyze and test the proposed inverter in the practical applications, its performance has been investigated in the grid-tied PV systems. In the proposed five-level inverter, the PCC method is implemented to obtain the switching pattern and control the active and reactive powers [30]. The schematic diagram of the applied control system for grid-tied application has been illustrated in Fig. 7. In this system, the reference injected current has been obtained based on the reference value of power ( $P_{ref}$ ) and the reference reactive power ( $Q_{ref}$ ). In addition, the magnitude and phase of the grid values have been obtained by the implemented phase-locked loop (PLL). Therefore, the current reference value and injected value have been compared in the current controller block and based on the PCC strategy, the appropriate gate pulses have been generated.

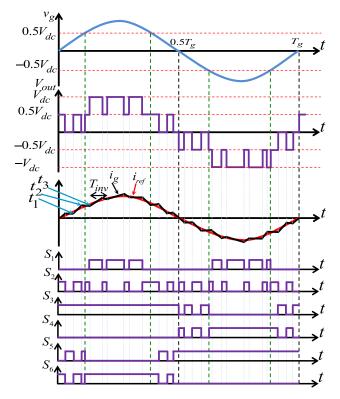

The reference and measured currents with the switches gate pulses have been shown in Fig. 8. In the current controller block, a special sampling time has been selected ( $T_{samp}$ ). It should be mentioned that, the power switches work with different switching frequencies. As a result, two different frequencies can be described for the proposed inverter: the switches average switching frequency ( $f_{avg}$ ) and the switching frequency of the inverter that can be seen from the load side ( $f_{inv}$ ). The instantaneous slop of the output inductor current that acts like an L-type filter can be calculated by reflecting the switching frequency of the inverter. In this inverter, the switching frequency of the inverter is equal or less than the half of the sampling frequency. In the other word, the maximum switching frequency of the inverter is equal to half of the sampling frequency.

FIGURE 7. Control system of the proposed grid-tied inverter.

By comparing the measured and reference waveforms of the output inductor current which is the injected grid current  $(i_g)$ , the switching pattern can be derived. During the positive half cycle, if the magnitude of the output voltage is less than half of DC link voltage  $(V_{dc}/2)$  for a certain sampling time  $(t_1)$  and the injected grid current is less than its reference value, the power switches  $S_2$ ,  $S_3$ , and  $S_6$  will start to conduct. Therefore, the output inductor current starts to increase linearly (First operational mode). In the next sampling period, if the injected grid current is more than its reference value  $(t_2)$ , so the power switches  $S_3$  and  $S_5$  will be turned on and the output inductor current will be reduced (Second operational mode). Also, if the grid voltage  $(V_g)$  is higher than half of the DC link voltage  $(V_{dc}/2)$ , the switching pattern will be different. In this condition, for a certain sampling time  $(t_3)$ , if the injected grid current is lower than its reference value, the power switches  $S_1$ ,  $S_3$ , and  $S_6$  will be turned on (Third operational mode). In addition, at a certain

FIGURE 8. Reference and measured current with switches gate pulses.

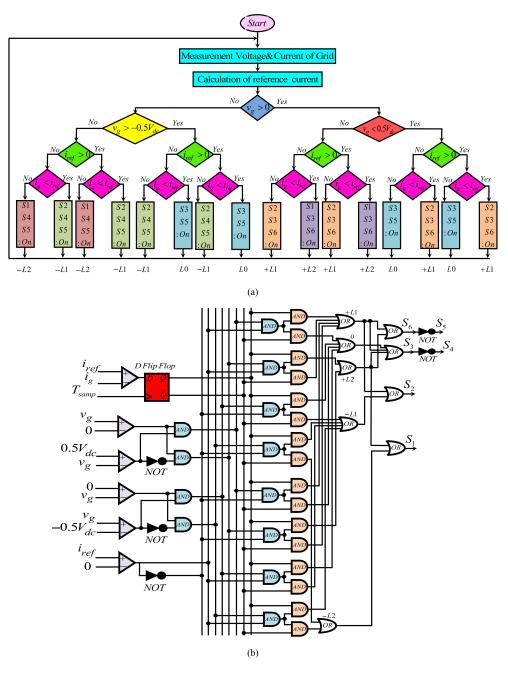

sampling time ( $t_4$ ), if the injected grid current is higher than the reference value, in order to decrease the output inductor current, the power switches  $S_2$ ,  $S_3$ , and  $S_6$  will be in on state (First operational mode). Also, in the negative half cycle, the switching pattern of the power switches can be obtained in a similar way. The flowchart of the implemented PCC strategy and logic circuit of the proposed method have been illustrated in Fig. 9(a) and (b). Based on this figure, by implementing this PCC strategy [31], the injected grid current is capable of tracking the reference current sinusoidal waveform properly.

In the third operational mode, considering the Volt-Second-Balance for the output inductor voltage waveform at a certain sampling period, the duty cycle and voltage gain of the inverter can be obtained as follows:

$$v_g = V_{m,g}\sin(\omega t) \tag{38}$$

$$i_g = I_{\rm m,g} \sin(\omega t - \varphi) \tag{39}$$

$$\int_{0}^{D_{inv}T_{inv}} \left( V_{dc} - v_g \right) dt + \int_{D_{inv}T_{inv}}^{T_{inv}} \left( V_{dc}/2 - v_g \right) dt = 0 \quad (40)$$

$$D_{inv} = \frac{V_{m,g}\sin(\omega t) - V_{dc}/2}{V_{dc}}$$

(41)

$$G = \frac{v_g}{V_{dc}} = D_{inv} + 1 \tag{42}$$

where  $\varphi$ ,  $D_{inv}$ ,  $V_{m,g}$ , and  $I_{m,g}$  are the angle between the injected voltage and current, duty cycle of inverter, gird voltage pick value, injected current pick value, respectively.

#### **III. DESIGN OF THE IMPLEMENTED COMPONENTS**

In this section, the inductance values of output filter and inductor  $L_1$ , and  $L_2$  are calculated. Also, the capacitance values of the capacitors  $C_1$ , and  $C_2$  are calculated in the following:

#### A. INDUCTANCE VALUE OF OUTPUT FILTER

In this section, design of the implemented output inductor  $L_f$  has been presented.

$$L_f = L_{f1} + L_{f2}, \qquad L_{f1} = L_{f2} = L_f/2$$

(43)

The output inductor current during a switching period can be written as follows:

$$i_{Lf}(t) = \frac{1}{L_f} \int_0^t V_{Lf}(t) dt + i_{Lf}(0)$$

(44)

Now, considering (40), the current ripple of the output inductor can be written as follows:

$$\begin{cases} \Delta i_{L_f} = \frac{1}{L_f} \int_{0}^{D.T_{inv}} (V_{dc} - v_g) dt \\ \Delta i_{L_f} = \frac{(V_{dc} - v_g) D_{inv}}{L_f f_{inv}} \end{cases}$$

(45)

The inductance value of output filter can be calculated based on the inverter frequency and duty cycle as follows:

$$L_f = \frac{(V_{dc} - v_g)D_{inv}}{\Delta i_{Lf} f_{inv}}$$

(46)

By substituting (41) into (46), the output inductor value can be obtained in terms grid voltage and DC link voltage as follows:

$$L_f = \frac{V_{dc}/2}{f_{inv} \Delta i_{Lf}} \left( 3v_g - V_{dc} - \left(\frac{v_g}{V_{dc}/2}\right)^2 \right)$$

(47)

Therefore, considering (43), the values of the inductors  $L_{f1}$  and  $L_{f2}$  will be the half of the  $L_f$  value.

#### B. INDUCTANCE VALUE OF INDUCRORS L1, AND L2

To calculate the inductance values of inductors  $L_1$ , and  $L_2$  it is necessary to write the integral equations of the inductors current for a complete switching cycle as:

$$i_{Li}(t) = \frac{1}{L_i} \int_0^t V_{Li}(t) dt + i_{Li}(0) \quad ; \quad i = 1, 2$$

(48)

By replacing (20) in (32) the inductance value of inductor  $L_2$  can be obtained as:

$$L_2 = \frac{D_{boost}.V_{Li}}{\Delta I_{Li}.f_{SW}} \tag{49}$$

Note that, the duty cycle of DC-DC boost converter can be calculated as:

$$D_{boost} = \frac{V_{Ci} - V_{dc}}{V_{Ci}} \tag{50}$$

FIGURE 9. (a) Flowchart of the applied PCC strategy (b) logic circuit of the applied PCC strategy.

By placing (50) in (49) and considering the maximum value of current ripple for each inductor ( $\Delta I_{Li,max}$ ), the final inductance value of each inductor can be obtained as:

$$L_i = \frac{V_{Ci} \cdot V_{dc}}{(V_{dc} + V_{Ci}) \cdot \Delta I_{Li,\max} \cdot f_{SW}}$$

(51)

In the DC-DC boost converter, the passing current of inductor can be calculated as:

$$I_{Li} = \frac{I_{out}}{1 - D_{boost}} \tag{52}$$

The stored energy of each inductor  $(L_1 \text{ and } L_2)$  can be obtained as follows:

$$W_{Li} = \frac{1}{2}L_i I_{Li}^2 = \frac{1}{2}L_i \left(\frac{I_{out}}{1 - D_{boost}}\right)^2 \quad ; \quad i = 1, 2 \quad (53)$$

$$W_{Li} = P_{out} \cdot t = \frac{P_{out}}{f_{SW}}$$

;  $i = 1, 2,$  (54)

Using (53) and (54), the inductance equation of  $L_2$  can be obtained as follows:

$$L_{i} = \frac{2 \left(1 - D_{boost}\right)^{2} . V_{Ci}^{2}}{f_{SW} . P_{out}} \quad ; \quad i = 1, 2$$

(55)

Regarding (50), the inductance values of each inductor ( $L_1$  and  $L_2$ ) can be obtained based on the average value of output power ( $P_{out}$ ), input voltage and switching frequency and expressed as follows:

$$L_{i} = \frac{2 (V_{dc})^{2}}{f_{SW}.P_{out}} \quad ; \quad i = 1, 2$$

(56)

# C. INDUCTANCE VALUE OF OUTPUT FILTER

Considering Fig. 3 (b), in the third operation mode (see Fig. 2(c)) the passing current of the capacitor  $C_1$  and  $C_2$  are equal to the injected grid current  $(i_g)$ . The voltage of capacitors can be obtained as:

$$V_{C1} = V_{C2} = \frac{1}{C} \int_0^t i_C(t) dt + V_C(0)$$

(57)

$$\Delta V_{C1} = \Delta V_{C2} = \frac{i_g}{C_1 f_{inv}} \cdot \left(\frac{v_g - V_{DC,link}}{V_{DC,link}}\right)$$

(58)

The peak value of ripple for each capacitor  $C_1$  and  $C_2$  are obtained when the voltage of the grid and the inductor  $L_f$  are been at the maximum point. Therefore, the value of capacitors  $C_1$  and  $C_2$  can be written as:

$$C_1 = C_2 = \frac{\mathrm{I}_{m,g}}{2\Delta V_{C,\max}f_{inv}} \cdot \left(\frac{V_{m,g} - V_{DC,link}}{V_{DC,link}}\right)$$

(59)

So, the final capacitance values of capacitors  $C_1$ , and  $C_2$  can be obtained as:

$$C_1 = C_2 = \frac{\mathrm{I}_{m,g}}{2\Delta V_{C,\max}f_{inv}} \cdot \left(\frac{V_{m,g} - V_{dc}}{V_{dc}}\right) \tag{60}$$

## **IV. POWER LOSS ANALYSIS**

In the proposed inverter, the total loss is equal to the summation of the component's conduction losses, switching losses, and power losses of passive components such as inductors and capacitors. As a result, total losses can be obtained as follows:

$$P_{Total} = P_C + P_S + P_{L,total} + P_{Cap,total}$$

(61)

#### A. CONDUCTION LOSSES

In the proposed inverter, the total conduction losses contain conduction losses of the power switches, power diodes, and implemented capacitors. Therefore, the average conduction losses of the proposed inverter can be calculated as follows:

$$P_{C,avg} = \left[\frac{s(t)}{\pi} \int_0^{\pi} \left(V_S i(t) + R_S i^{\gamma+1} d\omega t\right)\right] \\ + \left[\frac{c(t)}{\pi} \int_0^{\pi} R_{Cap} i^2(t) d\omega t\right] \\ + \left[\frac{d(t)}{\pi} \int_0^{\pi} \left(R_D i^2(t) + V_D\right) d\omega t\right]$$

(62)

where  $V_s$  and  $V_D$  are on-state drop voltage of the power switches and diodes, respectively.  $R_s$ ,  $R_{cap}$ , and  $R_D$  are the internal resistances of the power switches, capacitors, and power diodes, respectively. Also,  $\gamma$  is a constant parameter which is related to the internal structure of the power switches. s(t), d(t), and c(t) are the number of the power switches, power diodes, and capacitors, respectively.

#### **B. SWITCHING LOSSES**

In the power switches, a shift from on-state to off-state or vice versa always causes the switching losses. The switching pulses, voltage and current waveforms, and the switching losses waveform of the power switches have been illustrated in Fig. 10. Considering this figure, the power switches turn-on  $(P_{S,on})$  and turn-off  $(P_{S,off})$  losses can be obtained as follows:

$$P_{S,on} = \frac{N_{on}.E_{S,on}}{T_s} = \frac{(N_{on}f_s)(V_SI_S)}{6}t_{on}$$

(63)

$$P_{S,off} = \frac{N_{off} \times E_{S,off}}{T_s} = \frac{(N_{off}f_s) \times (V_S I_S)}{6} t_{off}$$

(64)

where  $E_{s,on}$  and  $E_{s,off}$  are the turn-on and turn-off losses per each time of the switch's turn-on and turn-off, respectively.  $N_{on}$  and  $N_{off}$  are the number of the switch's turnon and turn-off per each time of the inverter's switching period. Therefore, the total switching losses can be written as follows:

$$P_S = P_{S,on} + P_{S,off} \tag{65}$$

#### C. POWER LOSSES OF USED PASSIVE COMPONENTS

In this section, the power losses of passive components such as inductors  $(L_1 \& L_2)$  and capacitors  $(C_1 \& C_2)$  and output filter inductors  $(L_{f1} \& L_{f2})$  are calculated. In order to calculate the power losses of inductors  $L_1$ , and  $L_2$ , the following equations should be considered:

$$P_{L1} = r_{L1} \times I_{L1,rms}^2 \tag{66}$$

$$P_{L2} = r_{L2} \times I_{L2,rms}^2 \tag{67}$$

where,  $I_{L1,rms}$  and  $I_{L2,rms}$  are the average value of passing current of inductors  $L_1$  and  $L_2$ , respectively. Also, in the above equations,  $r_{L1}$ , and  $r_{L2}$  are the internal resistance of the inductors  $L_1$ , and  $L_2$ , respectively.

FIGURE 10. Switching gate pulse, voltage and current waveforms of power electronic switches, and switching losses waveform.

TABLE 3. Comparison of the proposed five-level inverter with other similar topologies.

| Topology | Number of components |    |           |       | Nvdc  | Input<br>voltage | Voltage | Voltage  | Pout               | Total<br>volume      | Power<br>density | Total<br>cost | Cost/Pout | RPS | Eff  |

|----------|----------------------|----|-----------|-------|-------|------------------|---------|----------|--------------------|----------------------|------------------|---------------|-----------|-----|------|

|          | Nsw                  | ND | $N_{cap}$ | $N_L$ | 1 Vdc | (V) boosting     | gain    | (W)      | (cm <sup>3</sup> ) | (W/cm <sup>3</sup> ) | (\$)             | (%)           | KI 5      | (%) |      |

| [18]     | 8                    | 7  | 2         | 3     | 3     | 100              | Yes     | 2        | 600                | 854.21               | 0.71             | 284.3         | 47.39     | No  | 86   |

| [36]     | 8                    | 1  | 2         | 0     | 1     | 200              | Yes     | 2        | 1000               | 152.33               | 6.57             | 189.3         | 18.93     | Yes | N.R  |

| [37]     | 8                    | 1  | 3         | 0     | 1     | 160              | No      | 1        | 500                | 150.7                | 3.32             | 114.3         | 23        | Yes | N.R  |

| [33]     | 6                    | 0  | 1         | 0     | 1     | 200              | No      | 1        | 770                | 377.7                | 2.03             | 208.1         | 27        | Yes | N.R  |

| [35]     | 12                   | 0  | 4         | 0     | 1     | 50               | Yes     | 4        | 250                | 696.93               | 0.35             | 165.3         | 66.12     | No  | 92   |

| [38]     | 8                    | 1  | 2         | 0     | 1     | 50               | Yes     | 2        | 250                | 145.87               | 1.71             | 147.2         | 58        | Yes | 95.5 |

| [39]     | 5                    | 0  | 2         | 1     | 1     | 100              | Yes     | D / 1-D  | 200                | 1144.07              | 0.17             | 189.4         | 95        | Yes | 92.5 |

| [48]     | 8                    | 0  | 3         | 2     | 1     | 200              | Yes     | 2        | 600                | 239.17               | 2.51             | 164.9         | 0.27      | Yes | 98.3 |

| [34]     | 6                    | 3  | 2         | 1     | 1     | 60               | Yes     | 4        | 600                | 128.1                | 4.68             | 59.13         | 9.85      | N.R | N.R  |

| [6]      | 8                    | 4  | 3         | 2     | 2     | 100              | Yes     | 1.5      | 1000               | 537.5                | 1.86             | 151.8         | 15.18     | Yes | 95.5 |

| [40]     | 6                    | 2  | 2         | 0     | 1     | 200              | Yes     | 2        | 1000               | 240.25               | 4.16             | 250.2         | 25.2      | Yes | 97.5 |

| [41]     | 8                    | 3  | 4         | 2     | 1     | 200              | Yes     | 2.8      | 2000               | 906.93               | 2.21             | 694.9         | 34.74     | N.R | 91.0 |

| [42]     | 7                    | 1  | 1         | 1     | 1     | 200              | Yes     | 2        | 1000               | 387.34               | 2.58             | 165.8         | 16.58     | Yes | 98.8 |

| [43]     | 10                   | 4  | 2         | 2     | 2     | 200              | Yes     | 1.5      | 500                | 106.7                | 4.68             | 163.8         | 32.76     | N.R | 96.0 |

| [44]     | 9                    | 0  | 2         | 0     | 1     | 200              | Yes     | 2        | 1000               | 106.61               | 9.37             | 74.1          | 7.41      | Yes | 98.6 |

| [45]     | 6                    | 0  | 2         | 2     | 1     | 100              | Yes     | 2D / 1-D | 200                | 356.4                | 0.56             | 85.72         | 43        | No  | 94.5 |

| [46]     | 10                   | 0  | 1         | 1     | 1     | 100              | Yes     | 2        | 360                | 113.87               | 3.16             | 150.3         | 41.7      | No  | 97   |

| [47]     | 11                   | 0  | 2         | 2     | 1     | 360              | No      | 1        | 1000               | 228.2                | 4.38             | 135.1         | 13.51     | Yes | 97.9 |

| Proposed | 8                    | 2  | 2         | 2     | 1     | 100              | Yes     | 4        | 620                | 146.4                | 4.24             | 151.7         | 24.4      | Yes | 97.6 |

Regarding Fig. 1, equivalent internal resistance of the output filter inductor can be calculated as follows:

$$r_{Lf} = r_{Lf1} + r_{Lf2} (68)$$

Considering Fig. 2, it can be seen that the passing current through output filter is equal to injected current to the grid. So, the RMS value of passing current through the output filter can be obtained as:

$$I_{Lf,rms} = \left[\frac{1}{2\pi} \int_0^{2\pi} \mathbf{I}_{mg}^2 \sin^2\left(\omega t\right) \cdot d\omega t\right]^{1/2} = \frac{\mathbf{I}_{mg}}{\sqrt{2}} \quad (69)$$

Therefore, the power losses of the output filter can be calculated as follows:

$$P_{Lf} = r_{Lf} \times \left(\frac{\mathbf{I}_{mg}}{\sqrt{2}}\right)^2 \tag{70}$$

So, the total value of power losses of the used inductors in the proposed inverter can be obtained as:

$$P_{L,total} = P_{L1} + P_{L2} + P_{Lf} \tag{71}$$

In addition, to calculate the power losses of capacitors  $C_1$  and  $C_2$ , the following equations should be used:

$$P_{C1} = r_{C1} \times I_{C1,rms}^2 \tag{72}$$

$$P_{C2} = r_{C2} \times I_{C2,rms}^2 \tag{73}$$

So, the total power losses of the capacitors can be calculated as follows:

$$P_{Cap,total} = P_{C1} + P_{C2} \tag{74}$$

where,  $I_{C1,rms}$ , and  $I_{C2,rms}$  are the RMS values of passing currents of these capacitors. Also, in the above equations,  $r_{C1}$ , and  $r_{C2}$  are the internal resistance of the inductors  $C_1$ , and  $C_2$ , respectively.

#### **V. COMPARISON**

In this section, the proposed five-level inverter has been compared with some other similar five-level inverters. This comparison contains the number of implemented power switches, the number of implemented power diodes, the number of inductors and capacitors (except output filter), the number of required input DC sources, input voltage value (V), boosting capability, voltage gain, output power (P<sub>out</sub>), total volume (cm<sup>3</sup>), power density(W/cm<sup>3</sup>), total cost (\$), cost/P<sub>out</sub> (%), reactive power supporting (RPS), and efficiency (Eff (%)). It should be mentioned that, the power density of the proposed inverter and other compared topologies can be obtained as:

Power density (W/cm<sup>3</sup>) =

$$\frac{P_{\text{out}}(W)}{\text{Volume}(cm^3)}$$

(75)

In (75), Pout and volume are output power and total volume of each inverter. To calculate the total volume of each structure, the volume of each of the energy storage components (capacitors and inductor cores), the volume of semiconductors (switches and diodes), according to the data contained in the datasheet, have been added together numerically. The results of this comparison have been gathered in Table 3. Based on this table, the implemented power switches in [6], [18], [36], [37], [38], [41], and [48] to provide a five-level output voltage is equal to the proposed inverter. However, despite the proposed inverter, these structures need more than one DC input source. Also, despite the proposed inverter, inverters in [33] and [37] do not have the boosting capability. It should be noted that by adding additional boost converters to these structures, it is possible to add the boosting capability to them, but this approach can increase the number of implemented elements. Regarding Table 3, between most of the compared structures the proposed five-level grid-tied inverter has the maximum value of power density. The structures presented in references [18], [35], [45], and [46], unlike the proposed

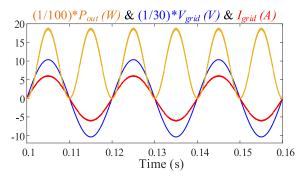

FIGURE 11. Output voltage (V<sub>out</sub>), grid current (V<sub>grid</sub>), and injected current into the grid (I<sub>grid</sub>): (a) at 0.7 leading PF, (b) 0.7 lagging PF, (c) under step change in the active power.

structure, do not have the ability to control reactive power. Also, the cost of constructing the laboratory prototype of the mentioned structures is higher than the proposed inverter. Therefore, the proposed structure is economically viable.

Finally, it can be concluded that among the compared structures, the proposed inverter can provide features such as voltage boosting capability, reactive power control, high power density in a lower volume and cost.

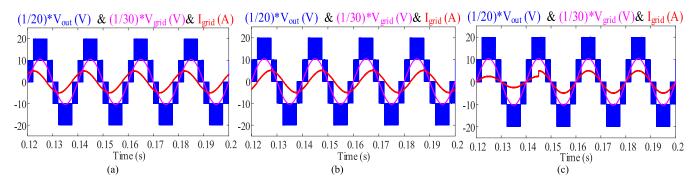

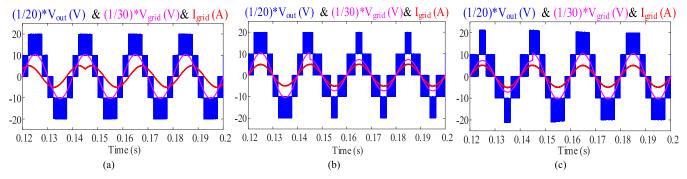

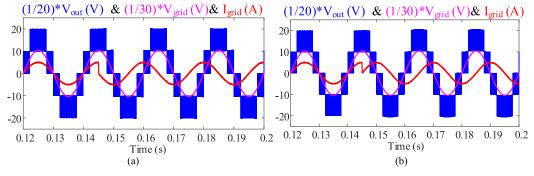

## VI. SIMULATION RESULTS TO VERIFY DYNAMIC RESPONSE OF THE PROPOSED INVERTER

In this section, to verify the accurate performance of the proposed five-level grid-tied inverter, the proposed inverter is simulated by using MATLAB/Simulink software. The simulation results are presented in different scenarios of injected active and reactive powers such as different conditions of power factor (PF), and step changes on the output active and reactive powers. Fig. 11 shows the output voltage (Vout), grid voltage (Vgrid), and also injected current to the grid  $(I_{grid})$ . Considering Fig. 11(a), it can be seen that the output voltage of the inverter and the grid voltage are in same phase. Also, the phase angle between the grid voltage and the injected current into the grid is 45 degrees. So, Fig. 11(a)illustrated the grid voltage and injected current into the grid at 0.7 leading PF. Also, Fig. 11(c) illustrates the output voltage (Vout), grid voltage (Vgrid) and injected grid current (Igrid) at unity power factor and step change on output active power. In Fig. 11(c), output power changes from 0.38 Kw to 0.77 Kw. Regarding Fig. 11(c), it can be verified that the proposed inverter along with its control system can support the step change on output power at unity PF. Fig. 12 (a) illustrates the output voltage, grid voltage and injected current to the grid under step change on phase angle of injected current to the grid. Regarding Fig. 12(a), the amplitude of the apparent power injected into the grid is constant and the step change has occurred in the phase angle of the injected grid current. In the other words, the operation of the inverter has changed from 0.7 leading PF condition to 0.7 lagging PF condition. Also, it can be verified that the proposed grid-tied inverter along with its control technique can support the step change on phase angle of injected current to the grid. Fig. 12(b) indicates the output voltage, grid voltage, and injected current to the grid waveforms under a step change on grid voltage. During this step change, the amplitude of grid voltage changes from 1 pu to 0.7 pu. However, during this step change in the grid voltage amplitude, the grid current maintains its steady state and follows its reference value. Also, Fig. 12(c) shows the output voltage, grid voltage, and injected current to the grid waveforms under a step change on grid voltage. During this step change, the amplitude of grid voltage changes from 0.7 pu to 1 pu. Considering Fig. 12(c), it can be seen that during this step change in the grid voltage amplitude, the grid current maintains its steady state and follows its reference value. Fig. 13 presents the output voltage, grid voltage and injected current to the grid under step change on phase angle of injected current to the grid. Based on Fig. 13(a), the phase angle changes from 0 degrees to 90 degrees. In the other words, the PF changes from 1 to zero with leading state. Under this condition, the proposed inverter absorbs the reactive power from the grid. Considering Fig. 13(b), the PF changes from 1 to zero with lagging state. Regarding this figure, the proposed inverter can only inject reactive power to the grid. Based on obtained simulation results, in addition to correct performance in non-unity power factor and in steady state, the inverter can also handle step change in non-unity PF.

In single-phase inverters, the injected power into the grid or load has a ripple twice the frequency of the grid voltage. In the case of the unit power factor, the instantaneous peak power injected into the grid is twice the average output power. Fig. 14 shows the grid voltage, grid current and injected power into the grid in the proposed inverter. It can be seen that the injected power into the grid has a frequency twice the frequency of the grid voltage. In order to be able to remove the power ripple from the input source, there are two methods:

- Active decoupled dc link

- Passive decoupled dc link.

In the active decoupled dc-link method, a separate dc-dc converter is needed to remove the power ripple from the input source [48], [49].

#### **VII. EXPERIMENTAL RESULTS**

In this section, in order to prove the theoretical analysis and the performance of the proposed five-level inverter, a 620 W laboratory prototype of this inverter has been assembled

FIGURE 12. Output voltage (V<sub>out</sub>), grid current (V<sub>grid</sub>), and injected current into the grid (I<sub>grid</sub>): (a) under step change on phase angle of injected current to the grid, (b) step change on V<sub>grid</sub> from 1 pu to 0.7 pu, (c) step change on V<sub>grid</sub> from 0.7 pu to 1 pu.

**FIGURE 13.** Output voltage ( $V_{out}$ ), grid current ( $V_{grid}$ ), and injected current into the grid ( $I_{grid}$ ) under step change on phase angel of the injected current to the grid: (a) step change from PF = 1 to PF = 0 with leading state, (b) step change from PF = 1 to PF = 0 with lagging state.

**FIGURE 14.** Grid voltage, grid current and injected power to the grid with double line frequency ripple.

| TABLE 4. List of | the implemented | components a | and required | descriptions |

|------------------|-----------------|--------------|--------------|--------------|

| of experimental  | prototype.      |              |              |              |

| Circuit Element                 | Туре                 | Explanatio<br>n           |  |  |

|---------------------------------|----------------------|---------------------------|--|--|

| S1, S2 S3, S4, S5, S6           | IPW65R041CFD         | 650 V/47 A                |  |  |

| Gate Driver                     | TLP 250              | IC                        |  |  |

| Power Diode                     | C3D10060A            | 600 V/30 A                |  |  |

| Current transducer              | LA55P                | Hall effect               |  |  |

| Sampling time                   | 25µs                 | -                         |  |  |

| Microcontroller                 | Beagle Bone<br>Black | ARM                       |  |  |

| Grid frequency                  | 50Hz                 | -                         |  |  |

| C1 & C2                         | Electrolytic         | 1000μ <i>F</i> -<br>250 V |  |  |

| L <sub>1</sub> & L <sub>2</sub> | Ferrite Core         | $100 \ \mu H$             |  |  |

| $L_{fl} = L_{f2}$               | Ferrite Core         | 1.4 <i>mH</i>             |  |  |

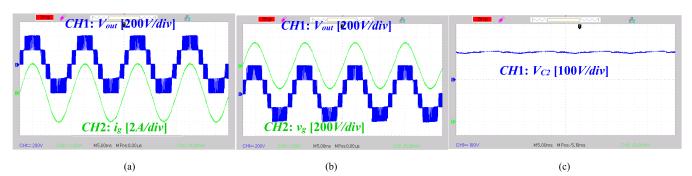

and its experimental results with the local grid have been extracted. In this prototype, the input power supply is 100 V and ARM microprocessor has been implemented to apply the PCC method. The values of the implemented parameter have been presented in Table 4. The output voltage of the inverter which is a Five-level voltage waveform with the sinusoidal injected grid current have been illustrated in Fig. 15(a). Based on Fig. 15(a), the proposed inverter is capable of tracking the reference current by the output voltage of the grid voltage waveform (50Hz) and the output voltage of the proposed inverter have been shown in Fig. 15(b). Considering

Fig. 15(b), it can be concluded that output voltage of the inverter is properly synchronized with local grid voltage. As a result, Fig. 15(b) proves the proper performance of the proposed inverter with the designed PCC method. In the proposed structure, the DC link voltage is controlled based on the output voltage pick value. The voltage waveforms of the capacitor  $C_2$  and DC link have been illustrated in Figs. 15 (c) and 16(a), respectively. Based on these figures,

FIGURE 15. Experimental results: (a) five-level output voltage waveform (200V/div) with injected grid current (2A/div) (b) five-level output voltage waveform (200V/div) with the local grid voltage (200V/div), (c) voltage of capacitor  $C_2$  (100 V /div).

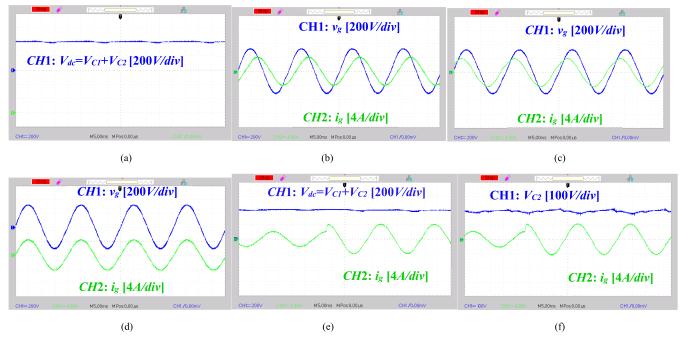

**FIGURE 16.** Experimental results: (a) voltage of DC link ( $V_{dc} = V_{C1} + V_{C2}$ ) (200V/div), Grid voltage waveform and the injected current to local grid: (b) grid voltage (200V/div) and injected grid current (4A/div) under lagging PF (c) grid voltage (200V/div) and injected grid current (4A/div) under lagging PF (d)grid voltage (200V/div) and injected grid current (4A/div) under unity PF, Dynamic performance of the proposed inverter under a step change in the amplitude of reference power ( $P_{ref}$ ): (e) voltage waveform of DC-link, (f) voltage across capacitor C<sub>2</sub>.

FIGURE 17. Dynamic performance of the proposed inverter under a step change in the amplitude of reference power (P<sub>ref</sub>): (a) Output voltage (200 V/div) and injected current (4 A/div); (b) Output voltage (200 V/div) and injected current (4 A/div).

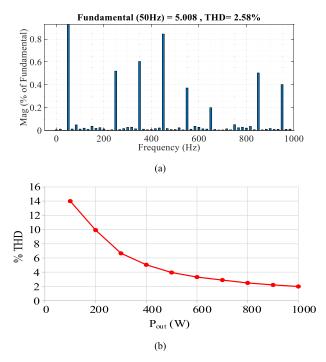

**FIGURE 18.** (a) Harmonic spectrum of the injected grid current, (b) THD of the grid current with the inverter operating at different power.

the voltage of capacitor  $C_2$  is equal to 200V which is the half of the output voltage pick value. The capacitors voltages have been controlled and their values have been regulated based on the output voltage pick value. Based on the measured input and output powers of the inverter, the efficiency of the inverter part is 97.6%. As mentioned, the performance of the proposed inverter has been tested with the local grid. As a result, the proposed inverter can support the reactive power.

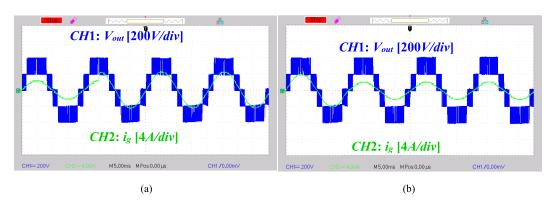

To prove this claim, the grid voltage and the injected grid current with different power factors including lagging, leading, and unit have been illustrated in Figs. 16(b)-16(d), respectively. These figures prove the capability of the proposed inverter with PCC method in generating sinusoidal injected current with different conditions of power factor. In order to investigate the dynamic response of the proposed inverter, step changes of the reference value of output power (Pref) have been applied. In order to investigate the dynamic response of the proposed inverter, step changes of the reference value of output power (Pref) have been applied. The experimental results of DC-link voltage and voltage of capacitor C<sub>2</sub>, under the mentioned step change are illustrated in Figs. 16(e) and (f), respectively. Considering these figures, the step change of the P<sub>ref</sub> is a change from 310 W to 620 W. Based on Figs. 16(e) and (f), the steady state voltage value of the DC-link and capacitor C2, are 400 V and 200 V, respectively. The output voltage and injected grid current under the step change are presented in Fig. 17(a). Based on this figure, the step change of the P<sub>ref</sub> is a change from 310 W to 620 W. The output voltage along with injected current to the grid under a step change of  $P_{ref}$  from 620 W to 310 W is

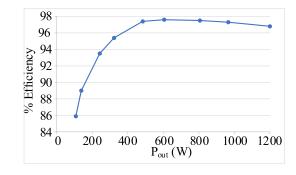

FIGURE 19. The efficiency curve of the proposed inverter working over the entire load range.

shown in Fig. 17(b). Based on the obtained results under the step change condition, it can be concluded that the proposed inverter has a good dynamic response under a step change. In addition, to investigate the total harmonic distortion (THD) grid current, the harmonic spectrum of the injected current to the grid is obtained by using MATLAB/Simulink software and illustrated in Fig. 18(a). Regarding Fig. 18(a), it can be seen that the THD of grid current is around 2.58 %. Based on IEC 61000-3-2 and IEEE 1547.2-2008 standards the limit of THD of injected current to the grid is less than 5%. Therefore, the proposed inverter can pass these mentioned standards. Also, Fig. 18(b) illustrates the THD of the injected current to the grid at the different output power of the inverter. Considering this figure, it can be seen that the THD of the grid current at 620 W output power is 2.58%. Also, paying attention to this figure, it can be seen that by increasing the generated output power of the inverter, the THD value of injected current to the grid decreases so, the quality of the injected power to the grid increases. Finally, the measured efficiency curve of the proposed inverter at different output powers (100 W~1200 W) is shown in Fig. 19. Considering Fig. 19, the maximum efficiency for the proposed inverter at 600 W is around 97.8%. Also, the efficiency of the proposed topology at 620 W is around 97.6 %.

#### **VIII. CONCLUSION**

In this paper, a five-level boost inverter with single DC source has been proposed. In the DC side of the proposed structure, a DC-DC boost converter has been implemented to transfer the required DC voltage from the single input DC source to the capacitors  $C_1$  and  $C_2$ . In this structure, the implemented PCC method to derive the switching pattern has been explained. In addition, design of the implemented components and power losses analysis have been presented. The performance of the proposed inverter in terms of different parameters have been compared to similar structures. Furthermore, in order to verify the claimed advantages of the proposed structure, a laboratory prototype of the proposed structure has been tested with the local grid. Both the injected active and reactive powers have been controlled based on the PCC method.

#### REFERENCES

- [1] N. V. Kurdkandi, M. G. Marangalu, S. Mohammadsalehian, H. Tarzamni, Y. P. Siwakoti, M. R. Islam, and K. M. Muttaqi, "A new six-level transformer-less grid-connected solar photovoltaic inverter with less leakage current," *IEEE Access*, vol. 10, pp. 63736–63753, 2022, doi: 10.1109/ACCESS.2022.3182240.

- [2] H. K. Jahan, H. Tarzamni, P. Kolahian, S. H. Hosseini, F. Tahami, and F. Blaabjerg, "A switched-capacitor inverter with optimized switchcount considering load power factor," in *Proc. IECON 45th Annu. Conf. IEEE Ind. Electron. Soc.*, Oct. 2019, pp. 4959–4964, doi: 10.1109/IECON.2019.8926785.

- [3] E. Babaei, H. Tarzamni, F. Tahami, H. K. Jahan, and M. B. B. Sharifian, "Multi-input high step-up inverter with soft-switching capability, applicable in photovoltaic systems," *IET Power Electron.*, vol. 13, no. 1, pp. 133–143, Jan. 2020.

- [4] M. Aalami, M. G. Marangalu, S. G. Zadeh, E. Babaei, and S. H. Hosseini, "Ladder-switch based multilevel inverter with reduced devices count," in *Proc. 11th Power Electron., Drive Syst., Technol. Conf. (PEDSTC)*, Feb. 2020, pp. 1–5.

- [5] K. Varesi, F. Esmaeili, S. Deliri, and H. Tarzamni, "Single-input quadruple-boosting switched-capacitor nine-level inverter with selfbalanced capacitors," *IEEE Access*, vol. 10, pp. 70350–70361, 2022, doi: 10.1109/ACCESS.2022.3187005.

- [6] Y. Suresh and A. K. Panda, "Investigation on hybrid cascaded multilevel inverter with reduced DC sources," *Renew. Sustain. Energy Rev.*, vol. 26, pp. 49–59, Oct. 2013.

- [7] S. H. Hosseini, A. Z. Gharehkoushan, and H. Tarzamni, "A multilevel boost converter based on a switched-capacitor structure," in *Proc. 10th Int. Conf. Electr. Electron. Eng. (ELECO)*, Bursa, Turkey, Nov. 2017, pp. 249–253.

- [8] E. Babaei, M. F. Kangarlu, and M. Sabahi, "Extended multilevel converters: An attempt to reduce the number of independent DC voltage sources in cascaded multilevel converters," *IET Power Electron.*, vol. 7, no. 1, pp. 157–166, Jan. 2014.

- [9] M. Farhadi-Kangarlu and M. G. Marangalu, "Five-level single-DC source inverter with adjustable DC-link voltage," in *Proc. Electr. Eng. (ICEE), Iranian Conf.*, May 2018, pp. 1017–1021.

- [10] M. Farhadi-Kangarlu and M. G. Marangalu, "A single DC-source fivelevel inverter applied in stand-alone photovoltaic systems considering MPPT capability," in *Proc. 10th Int. Power Electron., Drive Syst. Technol. Conf. (PEDSTC)*, Feb. 2019, pp. 338–342.

- [11] S. S. Lee, B. Chu, N. R. N. Idris, H. H. Goh, and Y. E. Heng, "Switchedbattery boost-multilevel inverter with GA optimized SHEPWM for standalone application," *IEEE Trans. Ind. Electron.*, vol. 63, no. 4, pp. 2133–2142, Apr. 2016.

- [12] M. S. W. Chan and K. T. Chau, "A new switched-capacitor boostmultilevel inverter using partial charging," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 54, no. 12, pp. 1145–1149, Dec. 2007.

- [13] M. R. Banaei, A. R. Dehghanzadeh, A. Fazel, and A. B. Oskouei, "Switching algorithm for single Z-source boost multilevel inverter with ability of voltage control," *IET Power Electron.*, vol. 6, no. 7, pp. 1350–1359, Aug. 2013.

- [14] N. Prabaharan and K. Palanisamy, "Analysis and integration of multilevel inverter configuration with boost converters in a photovoltaic system," *Energy Convers. Manage.*, vol. 128, pp. 327–342, Nov. 2016.

- [15] M. F. Kangarlu and E. Babaei, "Variable DC voltage as a solution to improve output voltage quality in multilevel converters," in *Proc. 4th Annu. Int. Power Electron., Drive Syst. Technol. Conf.*, Feb. 2013, pp. 242–247.

- [16] E. Babaei, M. F. Kangarlu, and M. Sabahi, "Dynamic voltage restorer based on multilevel inverter with adjustable DC-link voltage," *IET Power Electron.*, vol. 7, no. 3, pp. 576–590, Mar. 2014.

- [17] G. Mondal, K. Gopakumar, P. N. Tekwani, and E. Levi, "A reduced-switchcount five-level inverter with common-mode voltage elimination for an open-end winding induction motor drive," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 2344–2351, Aug. 2007.

- [18] N. A. Rahim and J. Selvaraj, "Multistring five-level inverter with novel PWM control scheme for PV application," *IEEE Trans. Ind. Electron.*, vol. 57, no. 6, pp. 2111–2123, Jun. 2010.

- [19] Z. Li, P. Wang, Y. Li, and F. Gao, "A novel single-phase five-level inverter with coupled inductors," *IEEE Trans. Power Electron.*, vol. 27, no. 6, pp. 2716–2725, Jun. 2012.

- [20] M. k. Nguyen and T. T. Tran, "Quasi cascaded H-bridge five-level boost inverter," *IEEE Trans. Ind. Electron.*, vol. 64, no. 11, pp. 8525–8533, Nov. 2017.

- [21] Y. Zhang and L. Sun, "An efficient control strategy for a five-level inverter comprising flying-capacitor asymmetric H-bridge," *IEEE Trans. Ind. Electron.*, vol. 58, no. 9, pp. 4000–4009, Sep. 2011.

- [22] K. Hasegawa and H. Akagi, "Low-modulation-index operation of a fivelevel diode-clamped PWM inverter with a DC-voltage-balancing circuit for a motor drive," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3495–3504, Aug. 2012.

- [23] P. Roshankumar, P. P. Rajeevan, K. Mathew, K. Gopakumar, J. I. Leon, and L.G. Franquelo, "A five-level inverter topology with single-DC supply by cascading a flying capacitor inverter and an H-bridge," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3505–3512, Aug. 2012.

- [24] P. P. Rajeevan and K. Gopakumar, "A hybrid five-level inverter with common-mode voltage elimination having single voltage source for IM drive applications," *IEEE Trans. Ind. Appl.*, vol. 48, no. 6, pp. 2037–2047, Nov. 2012.

- [25] S. K. Saketi, P. Chaturvedi, and D. Yadeo, "A new fault tolerant single phase 5-Level inverter topology," in *Proc. 8th IEEE India Int. Conf. Power Electron. (IICPE)*, Dec. 2018, pp. 1–5.

- [26] S. P. Gautam, L. Kumar, S. Gupta, and N. Agrawal, "A single-phase five-level inverter topology with switch fault-tolerance capabilities," *IEEE Trans. Ind. Electron.*, vol. 64, no. 3, pp. 2004–2014, Mar. 2017.

- [27] E. Babaei, M. F. Kangarlu, M. Sabahi, and M. R. A. Pahlavani, "Cascaded multilevel inverter using sub-multilevel cells," *Electric Power Syst. Res.*, vol. 96, pp. 101–110, Mar. 2013.

- [28] P. Alavi, P. Mohseni, E. Babaei, and V. Marzang, "An ultra-high stepup DC–DC converter with extendable voltage gain and soft-switching capability," *IEEE Trans. Ind. Electron.*, vol. 67, no. 11, pp. 9238–9250, Nov. 2020.

- [29] V. Marzang, S. H. Hosseini, N. Rostami, P. Alavi, P. Mohseni, and S. M. Hashemzadeh, "A high step-up non-isolated DC–DC converter with flexible voltage gain," *IEEE Trans. Power Electron.*, vol. 35, no. 10, pp. 10489–10500, Oct. 2020.

- [30] N. Vosoughi, S. H. Hosseini, and M. Sabahi, "Single-phase commongrounded transformer-less grid-tied inverter for PV application," *IET Power Electron.*, vol. 13, no. 1, pp. 157–167, Jan. 2020.

- [31] N. Vosoughi, S. H. Hosseini, and M. Sabahi, "A new transformer-less fivelevel grid-tied inverter for photovoltaic applications," *IEEE Trans. Energy Convers.*, vol. 35, no. 1, pp. 106–118, Mar. 2020.

- [32] P. C. Loh, D. G. Holmes, and T. A. Lipo, "Implementation and control of distributed PWM cascaded multilevel inverters with minimal harmonic distortion and common-mode voltage," *IEEE Trans. Power Electron.*, vol. 20, no. 1, pp. 90–99, Jan. 2005.

- [33] H. Vahedi, P.-A. Labbé, and K. Al-Haddad, "Sensor-less five-level packed U-cell (PUC5) inverter operating in stand-alone and grid-connected modes," *IEEE Trans. Ind. Informat.*, vol. 12, no. 1, pp. 361–370, Feb. 2015.

- [34] F. Gao, "An enhanced single-phase step-up five-level inverter," *IEEE Trans. Power Electron.*, vol. 31, no. 12, pp. 8024–8030, Dec. 2016.

- [35] L. He and C. Cheng, "A flying-capacitor-clamped five-level inverter based on bridge modular switched-capacitor topology," *IEEE Trans. Ind. Electron.*, vol. 63, no. 12, pp. 7814–7822, Dec. 2016.

- [36] S. Kumari, A. Verma, N. Sandeep, U. Yaragatti, and H. Pota, "A five-level transformer-less inverter with self-voltage balancing and boosting ability," *IEEE Trans. Ind. Appl.*, vol. 57, no. 6, pp. 6237–6245, Nov. 2021.

- [37] G. V. Bharath, A. Hota, and V. Agarwal, "A new family of 1-φ fivelevel transformerless inverters for solar PV applications," *IEEE Trans. Ind. Appl.*, vol. 56, no. 1, pp. 561–569, Jan./Feb. 2019.

- [38] S. Kumari, A. K. Verma, S. N, U. R. Yaragatti, and H. R. Pota, "An eightswitch five-level inverter with zero leakage current," *IET Power Electron.*, vol. 14, no. 3, pp. 590–601, Feb. 2021.

- [39] M. T. Azary, M. Sabahi, E. Babaei, and F. A. A. Meinagh, "Modified single-phase single-stage grid-tied flying inductor inverter with MPPT and suppressed leakage current," *IEEE Trans. Ind. Electron.*, vol. 65, no. 1, pp. 221–231, Jan. 2018.

- [40] R. Barzegarkhoo, Y. P. Siwakoti, N. Vosoughi, and F. Blaabjerg, "Sixswitch step-up common-grounded five-level inverter with switchedcapacitor cell for transformerless grid-tied PV applications," *IEEE Trans. Ind. Electron.*, vol. 68, no. 2, pp. 1374–1387, Feb. 2021.

- [41] A.-V. Ho and T.-W. Chun, "Single-phase modified quasi-Z-source cascaded hybrid five-level inverter," *IEEE Trans. Ind. Electron.*, vol. 65, no. 6, pp. 5125–5134, Jun. 2018.

- [42] M. N. H. Khan, R. Barzegarkhoo, Y. P. Siwakoti, S. A. Khan, L. Li, and F. Blaabjerg, "A new switched-capacitor multilevel inverter with soft start and quasi resonant charging capabilities," *Int. J. Electr. Power Energy Syst.*, vol. 135, Feb. 2022, Art. no. 107412.

- [43] T. Tran and M. Nguyen, "Cascaded five-level quasi-switched-boost inverter for single-phase grid-connected system," *IET Power Electron.*, vol. 10, no. 14, pp. 1896–1903, Nov. 2017.

- [44] M. N. H. Khan, Y. P. Siwakoti, M. J. Scott, L. Li, S. A. Khan, D. D.-C. Lu, R. Barzegarkhoo, F. Sidorski, F. Blaabjerg, and S. U. Hasan, "A common grounded type dual-mode five-level transformerless inverter for photovoltaic applications," *IEEE Trans. Ind. Electron.*, vol. 68, no. 10, pp. 9742–9754, Oct. 2021.

- [45] O. Husev, C. Roncero-Clemente, E. Romero-Cadaval, D. Vinnikov, and S. Stepenko, "Single phase three-level neutral-point-clamped quasi-Zsource inverter," *IET Power Electron.*, vol. 8, no. 1, pp. 1–10, 2015.

- [46] S. S. Lee, C. S. Lim, Y. P. Siwakoti, and K.-B. Lee, "Dual-T-type five-level cascaded multilevel inverter with double voltage boosting gain," *IEEE Trans. Power Electron.*, vol. 35, no. 9, pp. 9522–9529, Sep. 2020.

- [47] X. Zhu, H. Wang, W. Zhang, H. Wang, X. Deng, and X. Yue, "A novel single-phase five-level transformer-less photovoltaic (PV) inverter," CES Trans. Electr. Mach. Syst., vol. 4, no. 4, pp. 329–338, Dec. 2020.

- [48] L. Zhang and X. Ruan, "Control schemes for reducing second harmonic current in two-stage single-phase converter: An overview from DC-bus port-impedance characteristics," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 10341–10358, Oct. 2019, doi: 10.1109/TPEL.2019.2894647.

- [49] L. Zhang, X. Ruan, and X. Ren, "Second-harmonic current reduction for two-stage inverter with boost-derived front-end converter: Control schemes and design considerations," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 6361–6378, Jul. 2018, doi: 10.1109/TPEL.2017.2746878.

**PEYMAN ALAVI** was born in Urmia, Iran, in 1994. He received the B.Sc. degree in power electrical engineering from Shahid Beheshti University, Tehran, Iran, in 2016, and the M.Sc. degree in power electronics from the Department of Electrical and Computer Engineering, University of Tabriz, in 2019. His research interests include softswitching methods, high-step-up power electronic converters, and designing and controlling power electronic converters.

**SAEIDEH KHADEM** (Member, IEEE) was born in Tabriz, Iran, in 1987. She received the B.Sc. and M.Sc. degrees in electrical engineering from the University of Tabriz, Tabriz, in 2013 and 2015, respectively. She is currently pursuing the Ph.D. degree in electrical engineering and industrial applied mathematics with California State University Long Beach, Long Beach, CA, USA. She is a Senior Advanced Electrical Engineer with Honeywell. Her research interests include power

electronics, PV inverters, DC–DC converters, electric vehicle motor and controller design, power management, and model predictive control.

**HADI TARZAMNI** (Student Member, IEEE) was born in Tabriz, Iran, in 1992. He received the B.Sc. and M.Sc. degrees (Hons.) in power electrical engineering from the Faculty of Electrical and Computer Engineering, University of Tabriz, Tabriz, in 2014 and 2016, respectively. He is currently pursuing the dual Ph.D. degree in power electronics engineering with the School of Electrical Engineering, Sharif University of Technology, Tehran, Iran, and the Department of Elec-

trical Engineering and Automation, Aalto University, Espoo, Finland. Since January 2021, he has been a Researcher with the Department of Electrical Engineering and Automation and the Department of Electronics and Nanoengineering, Aalto University. He has authored and coauthored more than 35 journals and conference papers. He also holds six patents in the area of power electronics. His research interests include power electronic converters analysis and design, DC–DC and DC–AC converters, high-step-up power conversion, soft-switching and resonant converters, and reliability analysis. He was a recipient of the Best Paper Award at the 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), in 2019. He has been awarded a three-year Aalto ELEC Doctoral School Grant, in 2021, and a Jenny and Antti Wihuri Foundation Grant, in 2022.

**ALI MEHRIZI-SANI** (Senior Member, IEEE) received the Ph.D. degree in electrical engineering from the University of Toronto, Toronto, ON, Canada, in 2011. He is currently an Associate Professor with Virginia Tech, Blacksburg, VA, USA. Previously, he was an Associate Professor with Washington State University, Pullman, WA, USA, and a Visiting Professor with the Graz University of Technology (TU Graz), Graz, Austria. From 2007 to 2011, he was a Connaught Scholar

with the University of Toronto. His research interests include the power system applications of power electronics and the integration of renewable energy resources. He was a recipient of the 2018 IEEE PES Outstanding Young Engineer Award, the 2018 ASEE PNW Outstanding Teaching Award, the 2017 IEEE Mac E. Van Valkenburg Early Career Teaching Award, the 2017 WSU EECS Early Career Excellence in Research, the 2016 WSU VCEA Reid Miller Excellence in Teaching Award, the 2011 NSERC Post-doctoral Fellowship, and the 2007 Dennis Woodford Prize, for his M.Sc. thesis. He is an Editor of IEEE TRANSACTIONS ON POWER SYSTEMS, IEEE TRANSACTIONS ON ENERGY CONVERSION, and IEEE POWER ENGINEERING LETTERS.

**MILAD GHAVIPANJEH MARANGALU** was born in Urmia, Iran, in 1992. He received the B.Sc. and M.Sc. degrees in power electrical engineering from Urmia University, Urmia, in 2014 and 2018, respectively. He has been a Visiting Researcher with the Department of Electrical Engineering and Mechatronics, Tallinn University of Technology, Tallinn, Estonia. He is currently a research assistant of power electronics. He has authored and coauthored 26 journals and conference papers. His

current research interests include multilevel inverter, grid-tied photovoltaic inverter, high-step-up power electronic converters, control system of the multilevel inverter, and renewable energy systems.

**NASER VOSOUGHI KURDKANDI** (Member, IEEE) was born in Bostanabad, East Azerbaijan, Iran, in 1989. He received the B.Sc. degree in electrical engineering from Islamic Azad University, South Tehran Branch, Tehran, Iran, in 2011, and the M.Sc. and Ph.D. degrees in electrical engineering and power electronics from the University of Tabriz, Tabriz, Iran, in 2014 and 2019, respectively. From 2019 to 2020, he was a Postdoctoral Researcher with the University of Tabriz. In 2020,

he joined the Tallinn University of Technology, Tallinn, Estonia, as a Postdoctoral Researcher. He has been a Postdoctoral Researcher with San Diego State University, since 2022. His current research interests include multilevel inverters, grid-connected PV inverters, DC–DC switched-capacitor and switched-inductor converters, fast charge station for electric vehicles, battery-based energy storage systems, and induction motor drives.