This is an electronic reprint of the original article. This reprint may differ from the original in pagination and typographic detail.

Mack, Iris; Rosta, Kawa; Quliyeva, Ulviyya; Ott, Jennifer; Pasanen, Toni; Vähänissi, Ville; Rad, Zahra Jahanshah; Lehtiö, Juha Pekka; Laukkanen, Pekka; Soldano, Caterina; Savin, Hele

Quantifying the Impact of AI Deposition Method on Underlying AI2O3/Si Interface Quality

*Published in:* Physica Status Solidi. A: Applications and Materials Science

*DOI:* 10.1002/pssa.202200653

Published: 01/10/2023

Document Version Publisher's PDF, also known as Version of record

Published under the following license: CC BY

Please cite the original version:

Mack, I., Rosta, K., Quliyeva, U., Ott, J., Pasanen, T., Vähänissi, V., Rad, Z. J., Lehtiö, J. P., Laukkanen, P., Soldano, C., & Savin, H. (2023). Quantifying the Impact of AI Deposition Method on Underlying Al2O3/Si Interface Quality. *Physica Status Solidi. A: Applications and Materials Science*, *220*(20), Article 2200653. https://doi.org/10.1002/pssa.202200653

This material is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

# Nanoelectronics and Its New Materials – A NEW ERA OF NANOSCIENCE

Nanoelectronics and Its New Materials -

Discover the recent advances in electronics research and fundamental nanoscience.

Nanotechnology has become the driving force behind breakthroughs in engineering, materials science, physics, chemistry, and biological sciences. In this compendium, we delve into a wide range of novel applications that highlight recent advances in electronics research and fundamental nanoscience. From surface analysis and defect detection to tailored optical functionality and transparent nanowire electrodes, this eBook covers key topics that will revolutionize the future of electronics.

To get your hands on this valuable resource and unleash the power of nanotechnology, simply download the eBook now. Stay ahead of the curve and embrace the future of electronics with nanoscience as your guide.

Seeing beyond

WILEY

# Quantifying the Impact of AI Deposition Method on Underlying Al<sub>2</sub>O<sub>3</sub>/Si Interface Quality

Iris Mack,\* Kawa Rosta, Ulviyya Quliyeva, Jennifer Ott, Toni P. Pasanen, Ville Vähänissi, Zahra Sadat Jahanshah Rad, Juha-Pekka Lehtiö, Pekka Laukkanen, Caterina Soldano, and Hele Savin

Oxide-semiconductor interface quality has often a direct impact on the electrical properties of devices and on their performance. Traditionally, the properties are characterized through metal-oxide-semiconductor (MOS) structures by depositing a metal layer and measuring the capacitance-voltage (C-V) characteristics. However, metal deposition process itself may have an impact on the oxide and the oxide-semiconductor interface. The impact of magnetron sputtering, e-beam evaporation, and thermal evaporation on an Al<sub>2</sub>O<sub>3</sub>/Si interface is studied, where atomic layer deposited (ALD) Al<sub>2</sub>O<sub>3</sub> is used, by MOS C-V and corona oxide characterization of semiconductors (COCOS) measurements. The latter allows characterization of the interface also in its original state before metallization. The results show that sputtering induces significant damage at the underlying  $Al_2O_3/Si$  interface as the measured interface defect density  $D_{it}$ increases from 10<sup>11</sup> to 10<sup>13</sup> cm<sup>-2</sup> eV. Interestingly, sputtering also generates a high density of positive charges  $Q_{tot}$  at the interface as the charge changes from  $-2 \times 10^{12}$  to  $+7 \times 10^{12}$  cm<sup>-2</sup>. Thermal evaporation is found to be a softer method, with modest impact on Dit and Qtot. Finally, Alnealing heals the damage but has also a significant impact on the charge of the film recovering the characteristic negative charge of Al<sub>2</sub>O<sub>3</sub> ( $\sim -4 \times 10^{12}$  cm<sup>-2</sup>).

I. Mack, K. Rosta, U. Quliyeva, J. Ott, T. P. Pasanen, V. Vähänissi, C. Soldano, H. Savin Department of Electronics and Nanoengineering Aalto University Tietotie 3, FI-02150 Espoo, Finland E-mail: macki@mailbox.org J. Ott Helsinki Institute of Physics

University of Helsinki Gustaf Hällströminkatu 2, FI-00014 Helsinki, Finland

Z. S. Jahanshah Rad, J.-P. Lehtiö, P. Laukkanen Department of Physics and Astronomy University of Turku Vesilinnantie 5, FI-20014 Turku, Finland

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/pssa.202200653.

© 2023 The Authors. physica status solidi (a) applications and materials science published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

#### DOI: 10.1002/pssa.202200653

# 1. Introduction

Oxide thin films, such as silicon oxide  $(SiO_2)$ , aluminum oxide  $(Al_2O_3)$ , or hafnium oxide (HfO<sub>2</sub>), are of great importance for the integrated circuit industry, as well as in many optoelectronic applications due to their intrinsic properties. For instance, they are often used as optical or insulation layers in devices<sup>[1-4]</sup> and they are capable of providing a high-quality interface with neighboring materials such as silicon. In electrical devices, a highquality interface possesses a low recombination rate, in other words, oxide films can reduce the recombination probability of charge carriers at the silicon surface, which is often referred to as surface passivation.[5-12]

Efficient surface passivation by oxide films is based on two different mechanisms. The first mechanism is to decrease the interface defect density ( $D_{it}$ ) at the oxide–semiconductor interface, by reducing the amount of dangling bonds.<sup>[13]</sup> For

this, SiO<sub>2</sub> is one of the most widely used oxide films in Si-based devices.<sup>[14]</sup> The second one is the so-called field-effect mechanism, which significantly reduces the electron or hole concentration at the oxide-semiconductor interface by means of a built-in electric field.<sup>[15]</sup> This internal electric field can be obtained by the presence of an increased electrical charge density  $(Q_{tot})$  at the oxide-semiconductor interface. A well-known material for this is Al<sub>2</sub>O<sub>3</sub>, which has a high negative fixed charge density. Combining a high  $Q_{tot}$  with a low  $D_{it}$  would be ideal, which can be obtained with Al<sub>2</sub>O<sub>3</sub>/SiO<sub>x</sub>/Si interface.<sup>[7]</sup> In this context, it is important to point out that Al<sub>2</sub>O<sub>3</sub> deposited by atomic layer deposition (ALD), possesses negative fixed charges regardless of whether the layer is deposited on H-terminated silicon or on silicon covered with a very thin SiO<sub>2</sub> layer.<sup>[15-17]</sup> Indeed, several studies have shown that an interfacial SiO<sub>2</sub> layer is formed between the Al<sub>2</sub>O<sub>3</sub> film and silicon, where the negative fixed charges are located.<sup>[7-23]</sup>

In addition to dielectric layers, semiconductor devices typically contain also metal layers, for example, to realize electric contacts. One main challenge is to maintain the high quality of the oxide and the oxide–semiconductor interface, even after metal layer deposition. Different metallization methods, for example,

physical vapor deposition (PVD) techniques, such as magnetron sputtering, electron beam (e-beam) evaporation, and thermal evaporation, introduce different types and quantity of damage. For instance, during magnetron sputtering, the substrate is bombarded by a variety of particles, such as low-energy argon ions from the plasma, sputtered metal atoms, or high-energetic electrons that generate electrically active damage in the underly-ing layers.<sup>[24-27]</sup> In *e*-beam evaporation, low-energy X-rays from the electrons evaporating the source material introduce defects in the metal-dielectric-semiconductor stack.<sup>[28-30]</sup> In comparison, thermal evaporation is considered as the softest PVD method for depositing metal contacts on oxide-semiconductor structures. Based on the above, it is generally known that the damage introduced by the described metallization methods is different; however, investigations on their effect on  $D_{it}$  and  $Q_{tot}$  are rather limited, as deep-level transient spectroscopy (DLTS) and electron-beam-induced current (EBIC) techniques are used to determine the nature of the defects and their influence on recombination.[24,26-31]

Despite the possible damage to the underlying layers, metal layers can also be used to improve interface quality. A known and widely used method to reduce the defect density at the oxide-silicon interface, when using aluminum (Al) as metal contact, is to perform a postdeposition anneal after the Al deposition.<sup>[5,32-34]</sup> This method was named Alneal by B. Deal as a combination of Aluminum and anneal, when first investigated in 1969.<sup>[34]</sup> The effect of Alnealing was further investigated, for example, by Kerr and Cuevas through photoconductance<sup>[14]</sup> and by W. Eades through DLTS.<sup>[35]</sup> Furthermore, Collett et al. studied that the effect can be enhanced by adding different ions at the Si-SiO<sub>2</sub> interface.<sup>[32]</sup> Setälä et al. observed that Alnealing can have an influence on the passivation performance of Al<sub>2</sub>O<sub>3</sub>.<sup>[36]</sup> Although it is known that Alnealing can efficiently reduce dangling bonds at the oxide-Si interface in some configurations, it has remained unresolved, if the Al deposition method influences the efficiency of Alnealing.

The electrical quality of the oxide-semiconductor interface is typically evaluated by capacitance–voltage (C-V) measurements, in which the semiconductor/oxide structure is integrated in a metal-oxide-semiconductor (MOS) capacitor by adding a patterned metal layer on top.<sup>[37]</sup> However, this C-V technique has also some drawbacks: it is necessary to prepare separate samples that require metal contacts, the contact area needs to be accurately geometrically defined, as this influences the fitting of the data, and to get quantitative results either both true low- and high-frequency data is needed or when using Terman method true high-frequency and theoretical C-V curves are needed.<sup>[38]</sup> Moreover, as the metal deposition is suspected to have an influence on the properties of the oxide-semiconductor interface, as stated earlier, the fabrication of MOS capacitors for the C-V measurements may influence the results and the measurement data does not necessarily represent the original interface. These limitations can be overcome using the corona oxide characterization of semiconductors (COCOS) method that is based on measuring the surface contact potential via Kelvin probe.[39,40] COCOS provides a great advantage, since it is a noninvasive contactless technique, it allows to characterizes the interface without the need of a metal electrode, and it is independent of the sample

geometry. Thus, COCOS represents an ideal tool to determine the nature of the oxide–semiconductor interface prior to metal deposition and throughout different device fabrication steps.<sup>[39,41]</sup>

In this article, we investigate the Al<sub>2</sub>O<sub>3</sub>/Si interface properties and how they are affected by different metallization methods. We present a quantitative comparison of the influence of magnetron sputtering, e-beam evaporation, and thermal evaporation. Aluminum is chosen as metal due to its common use in siliconbased device fabrication. We investigate  $Q_{tot}$  and  $D_{it}$  by transforming the Al<sub>2</sub>O<sub>3</sub>/Si stack into MOS capacitors for C-V measurements and by measuring it directly with the COCOS method. By comparing the results obtained by these two methods, we determine the influence the aluminum deposition method has on the electrical properties of the interface. Furthermore, we assess the advantages and disadvantages of the two measuring methods for the characterization of the oxide-Si interface quality. In addition, we investigate with COCOS what impact the Alneal process in comparison to annealing without Al on top has on  $D_{it}$  and  $Q_{tot}$  and whether the used metallization method has any impact on the efficiency of Alnealing.

# 2. Experimental Section

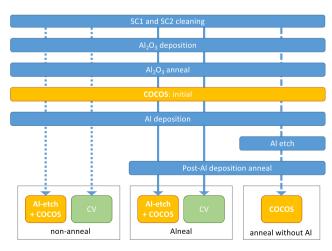

The experiments were performed on single-side polished p-type float-zone silicon wafers with  $3.00 \pm 2.00 \,\Omega$  cm resistivity. The wafer thickness was  $280 \pm 15 \,\mu$ m. The main process (blue) and characterization steps (green and yellow) are schematically presented in **Figure 1**.

The wafers were first cleaned using the SC1 and SC2 cleaning (SC1 standard clean:  $NH_4OH:H_2O_2:H_2O$  (1:1:5) at 80 °C for 10 min. SC2 standard clean:  $HCI:H_2O_2:H_2O$  (1:1:5) at 80 °C for 15 min) with an intermediate HF dip (HF:DIW 1:50). Then, ~22 nm-thick  $Al_2O_3$  films were deposited by ALD in a Beneq TFS-500 system, at a temperature of 200 °C, using trime-thylaluminium (TMA) and water ( $H_2O$ ) as precursors. Subsequently, the samples were annealed in a Centrotherm

**Figure 1.** Schematic of the processing steps, as well as the corresponding characterization steps. The yellow and green boxes indicate the COCOS and conventional *C*–*V* samples compared in this study.

furnace at 400 °C for 30 min in  $\rm N_2$  atmosphere (labeled "Al\_2O\_3 anneal" in Figure 1) to activate the surface passivation.

DVANCED

Afterward, an aluminum layer was deposited on the Al<sub>2</sub>O<sub>3</sub> film at room temperature by three different deposition methods: magnetron sputtering, *e*-beam evaporation, or thermal evaporation. The sputtered films were deposited at a base pressure of  $2.3 \times 10^{-7}$  mbar from a pure Al target driven at 2 kW DC power and with an argon (Ar) gas flow of 22 sccm. For *e*-beam evaporation, the base pressure was  $5 \times 10^{-7}$  mbar, the acceleration voltage 10 kV, and the beam current 20 mA. Thermal evaporation was performed at a base pressure of  $1.2 \times 10^{-6}$  mbar. The overall thickness of the Al films was around 200 nm for all deposition methods.

Following the Al deposition, most of the wafers were annealed at 400 °C for 30 min in N<sub>2</sub> atmosphere ("post-Al deposition anneal" in Figure 1). In other words, these wafers experienced the annealing step, which is commonly known as Alneal.<sup>[34]</sup> As a reference, in some of the samples, the Al layer was removed prior to exposing them to the same post-Al deposition anneal (dashed path in Figure 1). In these wafers, Al was removed using phosphoric acid-based Al etch mixture and the etching time was chosen in such a way that only aluminum and not the underlying Al<sub>2</sub>O<sub>3</sub> was removed.

Two methods were used to characterize the interface properties: conventional contact C-V measurements for MOS capacitor samples (green squares in Figure 1) and COCOS measurements for parallel produced samples, where the Al was removed before measuring (yellow squares). For the MOS capacitors, Al was deposited through a shadow mask with varying contact sizes from 0.008 to 7.1 mm<sup>2</sup>. The backside contact was realized by applying silver paste on the rear side of the wafer. C-V curves of the MOS capacitors were measured with a probe station<sup>[37]</sup> at 100 kHz and the obtained results for a single contact size were compared.

The COCOS method was based on external corona charge deposition on top of the oxide layer.<sup>[39,40]</sup> Therefore, it was necessary to remove the Al films prior to the COCOS measurements using the same Al etch as described earlier. The corona charge

was applied in small increments, from inversion to accumulation, and after each step the resulting contact potential difference was measured both in complete darkness and under strong illumination.<sup>[39]</sup> From these measurements, electrical parameters of the oxide–semiconductor stack such as flatband voltage ( $V_{\rm FB}$ ),  $Q_{\rm tot}$ , and  $D_{\rm it}$  were calculated. Every sample was measured in three different locations, and the range of variation is presented in each figure as error bars.

Conventional *C*–*V* measurements and COCOS were carried out on two sample types for comparison purposes: right after Al deposition (dotted path in Figure 1) and after the following post-Al anneal (solid path). As mentioned above, for the COCOS samples, the Al layer was removed prior to the measurements. The oxide charge ( $Q_{ox}$ ) in MOS capacitors, which is assumed to be located at the oxide–semiconductor interface, was determined by measuring the *C*–*V* curves from inversion to accumulation for p-type substrates. COCOS measurements were also performed from inversion to accumulation. The determined  $Q_{tot}$  was the total charge needed to achieve flatband condition starting from the initial state of the oxide–semiconductor system.

Additionally, COCOS allows characterization of the oxidesilicon interface right after  $Al_2O_3$  deposition (i.e., prior to the Al deposition) as well as of another sample type, where the Al layer was etched away before the sample obtained the post-Al deposition anneal (dashed line). These measurements were not possible with conventional MOS capacitors due to the absence of the metal layer.

#### 3. Results and Discussion

#### 3.1. Impact of Metal Deposition Method

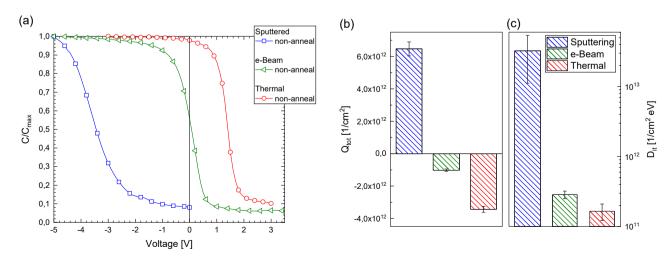

The impact of the different metallization methods on the  $Al_2O_3/Si$  interface was investigated by measuring the *C*–*V* characteristics from MOS capacitor samples, as well as by quantifying  $Q_{tot}$  and  $D_{it}$  from the corresponding COCOS samples. **Figure 2**a presents the *C*–*V* curves for MOS capacitors metallized by

**Figure 2.** Influence of different metallization methods for Al without postmetallization anneal on a) the C–V characteristics (CV non-anneal) of MOS capacitors, and b) the total charge  $Q_{tot}$  and c) the interface defect density  $D_{it}$  at midgap by COCOS measurements (COCOS non-anneal).

sputter deposition, *e*-beam, and thermal evaporation directly after the Al deposition (CV non-anneal). The curves were normalized to the largest value of each curve at accumulation.

IDVANCED

www.advancedsciencenews.com

The fast decrease of the capacitance in the *C*–*V* characteristics corresponds to the so-called flatband voltage ( $V_{FB}$ ), at which the energy bands of the substrate are becoming flat at the Al<sub>2</sub>O<sub>3</sub>/Si interface. The difference of  $V_{\rm FB}$  shows that the deposition method has a large impact on the amount and type of charge at the interface. The negative flatband voltage that is observed for the sputtered sample (blue, open squares) indicates that after Al sputtering, there are positive charges at the oxidesemiconductor interface. After metallization by e-beam evaporation (green, open triangles),  $V_{\rm FB}$  reaches near-zero voltage. This reveals that there is only little-to-no charge at the interface. However, after thermal evaporation (red, open circles), negative charge is found at the interface, which is expected due to the negatively charged Al<sub>2</sub>O<sub>3</sub>. From the flatband voltage shift, the oxide charge  $Q_{ox}$  at the oxide-semiconductor interface can be determined through

$$Q_{\rm ox} = -C_{\rm ox} \Delta V_{\rm FB} \tag{1}$$

where  $C_{\rm ox}$  is the capacitance of the oxide in accumulation and  $\Delta V_{\rm FB}$  the flatband voltage shift from neutrality (0 V) due to total oxide and interface charges.<sup>[42]</sup> For the investigated contacts, the derived  $Q_{\rm ox}$  is for the sputtered contacts (blue) (+10.9 ± 5.9) × 10<sup>12</sup> cm<sup>-2</sup>, whereas (-0.2 ± 0.3) × 10<sup>12</sup> cm<sup>-2</sup> for the *e*-beam evaporated (green) and (-2.1 ± 2.0) × 10<sup>12</sup> cm<sup>-2</sup> for thermal evaporated (red).

In Figure 2a it is also visible that the slope of the normalized C-V curves (i.e., the interface defect density) for the three metallization methods is different. The curves indicate that sputtering generates the highest  $D_{\rm it}$  (lowest slope), while thermal evaporation seems to be the least damaging leading to the lowest  $D_{\rm it}$  (steepest slope).

COCOS measurements were performed on sister samples to determine  $Q_{tot}$  and  $D_{it}$ .  $Q_{tot}$  is defined as

$$Q_{\rm tot} = Q_{\rm it}^{\rm FB} + Q_{\rm surf} + Q_{\rm ox} \tag{2}$$

where Q<sub>it</sub><sup>FB</sup> is the interface-trapped charge at flatband condition,  $Q_{\text{surf}}$  is any initial charge on the surface of the oxide, and  $Q_{\text{ox}}$  is the oxide charge. The results for  $Q_{tot}$  and  $D_{it}$  are given in Figure 2b,c, respectively. For the sputtered contact (blue), the total charge  $Q_{tot}$  is  $(+6.5 \pm 0.5) \times 10^{12} \text{ cm}^{-2}$ , whereas it is  $(-1.0\pm0.1)\times10^{12}\,\text{cm}^{-2}$  for e-beam (green) and  $(-3.4\pm0.2)\times$ 10<sup>12</sup> cm<sup>-2</sup> for thermally (red) evaporated aluminum. These values show the same trends as the above-described qualitative MOS and  $Q_{ox}$  results. They confirm that there are a large number of positive charges at the oxide-semiconductor interface for the sputtered and of negative charges for the thermal evaporated samples. While D<sub>it</sub> was more difficult to interpret from the C-V MOS results, Figure 2c indicates significant difference in the  $D_{it}$  at the Al<sub>2</sub>O<sub>3</sub>/Si interface for the three metallization methods. For the sputtered contact (blue), the defect density  $((3.3 \pm 2.2) \times 10^{13} \text{ cm}^{-2} \text{ eV})$  is more than two orders of magnitude higher than for the evaporated contacts: e-beam (green)  $(2.9 \pm 0.4) \times 10^{11} \, \mathrm{cm^{-2} \, eV}$ and thermal (red)  $(1.7 \pm 0.5) \cdot 10^{11} \text{cm}^{-2} \text{eV}.$

Taking into account the definition of  $Q_{tot}$  given in Equation (2), the differences in the determined values for  $Q_{tot}$  and  $Q_{ox}$  can be explained. The values for  $Q_{tot}$  are always larger, as they also include the interface-trapped charge ( $Q_{it}^{FB}$ ) and the initial surface charges ( $Q_{surf}$ ).  $Q_{surf}$  should be equal for all samples, as the preparation was identical. On the other hand,  $Q_{it}^{FB}$  should strongly depend on the deposition method, as the above determined  $D_{it}$  strongly varies for the different deposition methods. This is in line with the obtained values for  $Q_{tot}$  and  $Q_{ox}$ , as the difference between the two and the corresponding  $D_{it}$  is larger for the sputtered, than for the evaporated samples.

The obtained differences for the different metal deposition methods were expected to some extent, as it is known that, for example, during sputtering, the sample is bombarded with a variety of particles that can cause damage,<sup>[24–26]</sup> but the quantified amount is new. As reported by B. Deal, ionizing radiation of the plasma during sputter deposition generates electron–hole pairs in the oxide, which result in induced positive charge due to trapped holes.<sup>[34]</sup> However, it is still remarkable that sputtering generates  $D_{it}$  above  $1 \times 10^{13} \text{ cm}^{-2} \text{ eV}$ , as such high defect densities are not tolerable in devices.<sup>[43]</sup> This explains, why, curing steps such as annealing are in general introduced in fabrication processes.

#### 3.2. Impact of Alneal

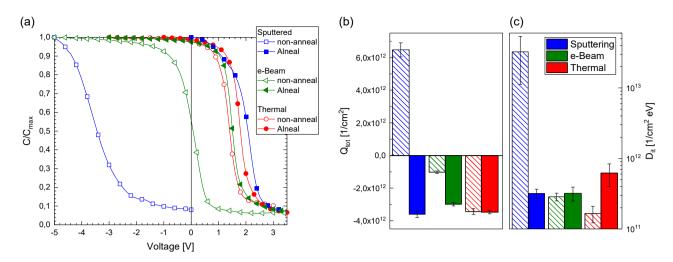

In SiO<sub>2</sub>/Si-based device fabrication, it is common to intentionally cover the oxide–semiconductor surfaces with aluminum and perform a post-Al anneal (Alneal) to improve the quality of the SiO<sub>2</sub>/Si interface.<sup>[14,32,34]</sup> To investigate the effect of the Alneal on the Al<sub>2</sub>O<sub>3</sub>/Si interface, we compared in **Figure 3**a the *C*–*V* results of Alnealed samples (CV Alneal: filled symbols) to the above-described as-deposited samples (CV non-anneal: open symbols).

Upon Alneal, all C-V curves shifted toward similar flatband voltages; therefore, the major differences for the different deposition methods discussed earlier have been reduced. In particular, we observed that 1) positive charges induced by Al sputter deposition are cancelled out and actually become negative and 2) the (negative) charge density of the e-beam evaporated sample is further increased. In addition, differences in the slopes have been reduced, indicating that the Alneal process is effective in recovering most of the damage (possibly all) induced by metal deposition and in reducing any intrinsic difference derived by the metal deposition method. These changes in the C-V curves also reflect in the values of  $Q_{ox}$  determined from them, leading to same values within the measurement accuracy of the method. In numerical numbers, the total charge after Alnealing for Al deposited by sputtering, e-beam, or thermal evaporation is  $(-4.0 \pm 3.1) \times 10^{12}$ ,  $(-1.8 \pm 2.0) \times 10^{12}$ , and  $(-3.1\pm2.6)\times10^{12}\,\text{cm}^{-2}\text{,}$  respectively.

The changes observed with the C-V curves are also reflected in the values of  $Q_{tot}$  and  $D_{it}$  measured with COCOS. By comparing the filled (COCOS Alneal) with the ruled (COCOS non-anneal) bars in Figure 3b, one can see that  $Q_{tot}$  at the oxide–silicon interface after Alnealing is about

**Figure 3.** Influence of post-Al deposition anneal (Alneal) on the oxide–semiconductor structure on a) the C-V characteristics for different metallization methods before (open symbols, CV non-anneal) and after Alnealing (filled symbols, CV Alneal). b) Total charge  $Q_{tot}$  and c) interface defect density  $D_{it}$  at midgap with respect to the influence of metallization method for non-anneal (ruled, COCOS non-anneal) and Alneal (filled, COCOS Alneal) samples.

$(-3.3 \pm 0.3) \times 10^{12} \,\mathrm{cm}^{-2}$  for all samples, independently of the prior metallization method. Upon Alneal, also the  $D_{\mathrm{it}}$  values are all within the same order of magnitude, independently of the deposition method, as shown in Figure 3c. This is in agreement with the changes in the slopes observed in the *C*–V curves in Figure 3a and the derived values given earlier. We note a non-negligible increase of the interface defect density after Alneal treatment for the thermally evaporated samples measured by COCOS; this unexpected change is currently under investigation.

Our experimental results demonstrate that even a large damage induced by metallization (as in the case of sputtering) can be cured by postmetallization annealing (Alneal) of the samples. According to B. Deal, the reduction of the positive charge due to trapped holes, induced by the plasma during sputtering, can be annealed out at 350 °C or higher.<sup>[34]</sup> The curing effect for D<sub>it</sub> by Alnealing was also expected to a certain extent, as reductions for Al/SiO<sub>2</sub>/Si-based structures are reported in earlier works.<sup>[5,15,19,34,43]</sup> Furthermore, a similar reduction in  $D_{it}$  of Al/Al2O3/Si MOS structures with sputtered Al films was recently reported by Khosla et al.<sup>[44]</sup> The improvement could be explained by hydrogen species, which diffuse to the oxide-semiconductor interface and terminate the dangling bonds at the interface, as done for SiO<sub>2</sub>/Si interfaces.<sup>[5,32,34,43,45]</sup> Those hydrogen species form, when water, introduced to the system as traces of moisture, reacts with the Al during annealing. Water traces are introduced at different points throughout the process and can therefore be at the Al–oxide interface, in the Al or on the Al surface.<sup>[5,32,34,43,45]</sup> The beneficial impact of Alnealing has also been observed, when using SiO<sub>2</sub>/TiO<sub>2</sub> as oxide in metal-oxide-semiconductor thinfilm stacks,<sup>[32,33]</sup> which supports the assumption that the same theory could also be applied for our Al<sub>2</sub>O<sub>3</sub>/Si interface. In summary, the above-discussed experiments have shown that Alnealing not only reduces the  $D_{it}$  at the oxide-semiconductor interface, but also significantly changes the charge density Q<sub>tot</sub>.

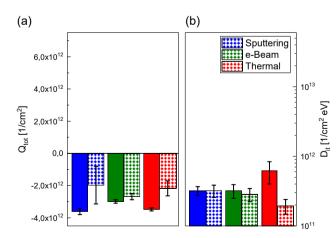

Figure 4. Initial values for total charge  $Q_{tot}$  and interface defect density  $D_{it}$  at midgap for 22 nm-thick Al<sub>2</sub>O<sub>3</sub> measured directly after oxide deposition and Al<sub>2</sub>O<sub>3</sub> anneal (COCOS initial).

#### 3.3. Initial Properties of the $Al_2O_3/Si$ Interface

We further used COCOS characterization to study the initial stage (before metallization) of the studied Al<sub>2</sub>O<sub>3</sub>/Si interface right after activating the surface passivation (Al<sub>2</sub>O<sub>3</sub> anneal). The measured values for  $Q_{\rm tot}$  ((-2.4 ± 0.2) × 10<sup>12</sup> cm<sup>-2</sup>) and  $D_{\rm it}$  ((4.6 ± 2.1) × 10<sup>11</sup> cm<sup>-2</sup> eV) (COCOS initial) are presented in **Figure 4**, and are consistent with literature.<sup>[15,20-22,46]</sup>

When comparing with the corresponding  $Q_{tot}$  after metal deposition (Figure 2), it becomes clear that the initial value is intermediate between the values after *e*-beam and thermal evaporation. On the other hand, if we compare the initial  $D_{it}$  to  $D_{it}$  of thermal and *e*-beam evaporated samples, it seems that deposition of Al by evaporation actually improves the Al<sub>2</sub>O<sub>3</sub>/Si interface. When comparing the obtained initial values in Figure 4 to the values given in Figure 3 for the Alnealed samples, it becomes

visible that by Alnealing of the oxide–semiconductor interface, the characteristic negative charge of Al<sub>2</sub>O<sub>3</sub> can be increased by  $\Delta Q_{\rm tot} = \sim 1 \times 10^{12} \, {\rm cm}^{-2}$  and that  $D_{\rm it}$  changes back to the value of the initial stage. A similar increase of  $Q_{\rm tot}$  was also observed by Setälä et al. for n-type Si-wafers, and they also observe a decrease for  $D_{\rm it}$  after Alnealing.<sup>[36]</sup>

#### 3.4. Impact of Presence of Al Layer During Alneal

IDVANCED

In the sections above, we have demonstrated that Alnealing is effective for healing damage induced by metal deposition. However, it remains unclear if this effect is a direct consequence of the annealing process itself or possibly related to the physical presence of the Al layer during annealing. COCOS allows us to gain a deeper insight in this subject. Samples which have undergone the same anneal process (as Alnealed samples) after the aluminum layer was removed (COCOS anneal) were prepared and characterized. Figure 5 shows the effect of the annealing process with and without Al layer, filled and dotted bars, respectively. Our results suggest that the value of Q<sub>tot</sub> depends on the presence of the Al film during the thermal treatment, independently of the deposition method, the absolute value of Q<sub>tot</sub> is consistently smaller after annealing (COCOS anneal - dotted) than after Alnealing (COCOS Alneal - filled). In addition, when comparing  $Q_{tot}$  after annealing with the initial values (Figure 4), it is clear that the values after annealing without Al (COCOS anneal) are closer to the initial value than after Alnealing. Therefore, we can conclude that the annealing process by itself (at 400 °C in pure N<sub>2</sub> atmosphere) has a positive effect, as it reduces the positive charges induced by Al deposition. This is consistent with work reported by B. Deal, as he has reported earlier that plasma-induced positive charge can be cured by annealing at temperatures higher than 350 °C.<sup>[34]</sup> Furthermore, the investigation of Q<sub>tot</sub> shows that it is enough to anneal after metal deposition to regain the original strength of field-effect passivation. On the other hand, for further improvement in field-effect

**Figure 5.** Effect of postmetal deposition anneal on samples with and without the aluminum layer. a)  $Q_{tot}$  and b)  $D_{it}$  after postmetal annealing with aluminum (filled: COCOS Alneal) or without aluminum (dotted: COCOS anneal) on the oxide measured by the COCOS method.

passivation, it is desirable to increase negative charges at the interface; thus, Alnealing is in this case the preferred choice.

Regarding the interface defect density, the effect is quite surprisingly overall less clear (Figure 5b) even though Alnealing was introduced to improve the oxide–semiconductor interface. The results indicate negligible differences between Alnealing and annealing for the sputter-deposited (blue) or *e*-beam-evaporated (green) samples. In the case of thermally evaporated films (red), a more pronounced difference in  $D_{it}$  is observed. This behavior is currently investigated further. We also note that independently of the annealing process (i.e., with or without Al on the surface),  $D_{it}$  values are smaller than the measured initial value (Figure 4), except for the thermally evaporated Alnealed sample (red filled). This could indicate that in the case of ALD-deposited Al<sub>2</sub>O<sub>3</sub>, the dissociation of water by Al during the Alnealing is less important, as the Al<sub>2</sub>O<sub>3</sub> layer already contains a remarkable amount of hydrogen that can heal dangling bonds at the interface.<sup>[6]</sup>

#### 3.5. Discussion and Summary

The systematic investigation presented here demonstrates that the metallization method influences the characteristics of oxide–semiconductor interfaces. **Table 1** summarizes the obtained values for  $Q_{tot}$  and  $D_{it}$  for the different deposition methods and the various processes measured with the COCOS method.

By preparing identical samples, where only the Al deposition method was varied, we confirmed that sputtering indeed induces a high amount of damage at the interface, which can be seen in the high  $D_{\rm it}$  value. Furthermore, thermal evaporation can be considered as the least damaging method among the three PVD deposition techniques investigated. On the other hand, when comparing the non-anneal values for  $Q_{\rm tot}$  with the initial values obtained for the pure Al<sub>2</sub>O<sub>3</sub>/Si interface (before any Al deposition), it becomes clear that the total negative charge at the oxide–semiconductor interface, which is needed for the field-effect passivation, is reduced during the Al deposition by sputtering or *e*-beam evaporation, whereas it is increased during thermal evaporation.

The exact generation of the damage at the interface was not investigated in this article, if it is only the bombardment by different species during metal deposition, as suggested in literature,<sup>[24–26,28–30]</sup> or if it is the induced temperature during the metal deposition. Nevertheless, the just described factors should have an influence on the absolute values, especially if

**Table 1.** Summary of total charge  $Q_{tot}$  and interface defect density  $D_{it}$  for Al<sub>2</sub>O<sub>3</sub>-passivated samples after Al deposition via different methods and anneal processes, as investigated by COCOS method. (\* This unexpected value is currently under investigation).

|                     | $Q_{\rm tot}  [10^{12}  {\rm cm}^{-2}]$ |                |         | $D_{\rm it}~[10^{11}~{\rm eV^{-1}~cm^{-2}}]$ |                |         |

|---------------------|-----------------------------------------|----------------|---------|----------------------------------------------|----------------|---------|

|                     | Sputtering                              | <i>e</i> -beam | Thermal | Sputtering                                   | <i>e</i> -beam | Thermal |

| Initial (before Al) |                                         | -2.4           |         |                                              | 4.6            |         |

| Non-anneal          | 6.5                                     | -1.0           | -3.4    | 325.0                                        | 2.9            | 1.7     |

| Alneal              | -3.6                                    | -3.0           | -3.5    | 3.2                                          | 3.2            | 6.2*    |

| Anneal without Al   | -2.0                                    | -2.7           | -2.2    | 3.2                                          | 2.8            | 1.9     |

18626319, 0, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/pssa.20220653 by Aalto University, Wiley Online Library on [01/10/2023]. See the Terms and Conditions (https://onlinelibrary.wiley.com/terms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons Licenses

different metal contacts are used, as they should depend on the deposition parameters needed, such as power or pressure. This is further supported by the findings of Cho et al., who investigated the influence of process parameters when depositing a thin film by PECVD on top of  $Al_2O_3$ .<sup>[47]</sup> Furthermore, we have seen that for thin (12 nm)  $Al_2O_3$  the changes to  $Q_{tot}$  are more pronounced, although the tendencies are similar to those of the discussed thicker (22 nm)  $Al_2O_3$  films (results not presented in this article). Therefore, we think that we can assume that the observed phenomena could also be valid for other oxide–semiconductor interfaces, independent of the used materials.

Furthermore, the changes in  $Q_{tot}$  and  $D_{it}$  in comparison to their initial values can be influenced by annealing without metal or by Alnealing the oxide–Si interface. When only  $D_{it}$  is considered, there is no clear preference for annealing or Alnealing, as the differences are in the range of measurement fluctuations. On the contrary, if a high field effect, that is, a high  $Q_{tot}$ , is needed, which is even higher than the initial values, it is necessary to perform an Alneal.

Finally, the investigated influence of different metal deposition methods and the different annealing steps on the oxidesemiconductor interface show that the COCOS characterization possesses several benefits in comparison to using the second harmonic generation (SHG) method<sup>[48]</sup> or the traditional investigation by measuring *C*–*V* curves of MOS capacitors. First, there is no requirement to precisely know the sample geometry (SHG and MOS). Second, there is no need for electrical contacts (MOS). Instead, COCOS opens the possibility to assess the initial stage and therefore the influence of the contact deposition, as well as the impact of metal-free annealing in comparison to Alnealing of the oxide–semiconductor interface. Furthermore, reducing the number of process steps required has the advantage of limiting possible contamination.

#### 4. Conclusion

In this article, we systematically investigated the influence of different metallization methods on the characteristics of oxidesemiconductor interfaces by two different methods: on the device level by measuring C-V curves of MOS capacitors and on film level through the COCOS method. By measuring  $Q_{tot}$  and  $D_{it}$ , we have shown that magnetron sputtering introduces significant damage, whereas thermal evaporation is the softest method. Furthermore, we have demonstrated that Alnealing heals the damage as expected but rather surprisingly it has also a significant impact on the charge of the film recovering the characteristic high negative charge of Al<sub>2</sub>O<sub>3</sub>. However, if the anneal is performed without the presence of aluminum, Q<sub>tot</sub> is not fully recovered whereas D<sub>it</sub> returns to the original level. In summary, when characterizing interfaces and/or designing devices, one should keep in mind that metallization methods as well as annealing processes can affect the interface quality.

### Acknowledgements

I.M. and K.R. contributed equally to this study and should be considered joint first authors. The authors would like to thank Business Finland in the framework of the Silicon Surface Processing Commercialization

(SISUproco) project, the Academy of Finland (#331313, #338974), and Tandem Industry Academia funding from the Finnish Research Impact Foundation for financial support of the research. The work is related to the Flagship on Photonics Research and Innovation "PREIN" funded by Academy of Finland. Furthermore, the authors acknowledge the provision of facilities by Aalto University and VTT Technical Research Centre of Finland at OtaNano - Micronova Nanofabrication Centre and the technical support by Aalto's Nanofab team.

# **Conflict of Interest**

The authors declare no conflict of interest.

# **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **Keywords**

corona oxide characterization of semiconductors, defect density, interface quality, metal-oxide-semiconductors, physical vapor deposition, thin-film metallization

Received: September 19, 2022 Revised: July 23, 2023 Published online:

- J. Kim, J. Park, J. H. Hong, S. J. Choi, G. H. Kang, G. J. Yu, N. S. Kim, H.-E. Song, J. Electroceram. 2013, 300, 41.

- [2] X. Yu, T. J. Marks, A. Facchetti, Nat. Mater. 2016, 150, 383.

- [3] A. Prasad, S. Balakrishnan, S. K. Jain, G. C. Jain, J. Electrochem. Soc. 1982, 1290, 596.

- [4] S. K. Deb, Sol. Energy Mater. Sol. Cells 1992, 250, 327.

- [5] R. S. Bonilla, B. Hoex, P. Hamer, P. R. Wilshaw, Phys. Status Solidi A 2017, 2140, 1700293.

- [6] G. Dingemans, F. Einsele, W. Beyer, M. C. M. van de Sanden, W. M. M. Kessels, J. Appl. Phys. 2012, 1110, 093713.

- B. Hoex, J. Schmidt, P. Pohl, M. C. M. van de Sanden, W. M. M. Kessels, J. Appl. Phys. 2008, 1040, 0044903.

- [8] S. Huang, Q. Wu, Z. Jia, X. Jin, X. Fu, H. Huang, X. Zhang, J. Yao, J. Xu, Adv. Opt. Mater. 2020., 80, 1901808.

- [9] A. S. Mayet, H. Cansizoglu, Y. Gao, S. Ghandiparsi, A. Kaya, C. Bartolo-Perez, B. AlHalaili, T. Yamada, E. P. Devine, A. F. Elrefaie, S.-Y. Wang, M. S. Islam, *J. Opt. Soc. Am. B* 2018, 350, 1059.

- [10] H. J. Queisser, E. E. Haller, Science 1998, 2810, 945.

- P. Repo, J. Benick, V. Vähänissi, J. Schön, G. von Gastrow, B. Steinhauser, M. C. Schubert, M. Hermle, H. Savin, *Energy Proc.* 2013, *38*, 866.

- [12] P. Saint-Cast, Y.-H. Heo, E. Billot, P. Olwal, M. Hofmann, J. Rentsch, S. W. Glunz, R. Preu, *Energy Proc.* 2011, 8, 642.

- [13] S. Olibet, E. Vallat-Sauvain, C. Ballif, Phys. Rev. B 2007, 760, 035326.

- [14] M. J. Kerr, A. Cuevas, Semicond. Sci. Technol. 2001, 170, 35.

- [15] B. Hoex, J. J. H. Gielis, M. C. M. van de Sanden, W. M. M. Kessels, J. Appl. Phys. 2008, 1040, 113703.

- [16] V. Naumann, M. Otto, R. B. Wehrspohn, M. Werner, C. Hagendorf, Energy Proc. 2012, 27, 312.

#### **ADVANCED** SCIENCE NEWS

www.advancedsciencenews.com

- [17] F. Werner, in Atomic Layer Deposition of Aluminum Oxide on Crystalline Silicon: Fundamental Interface Properties and Application to Solar Cells, 2014, ISBN 978-3-8440-3039-6.

- [18] B. W. Busch, O. Pluchery, Y. J. Chabal, D. A. Muller, R. L. Opila, J. R. Kwo, E. Garfunkel, *MRS Bull.* **2002**, *270*, 206.

- [19] M. N. Getz, M. Povoli, E. Monakhov, J. Appl. Phys. 2021, 1290, 205701.

- [20] F. Werner, B. Veith, D. Zielke, L. Kühnemund, C. Tegenkamp, M. Seibt, R. Brendel, J. Schmidt, J. Appl. Phys. 2011, 1090, 113701.

- [21] N. M. Terlinden, G. Dingemans, M. C. M. van de Sanden, W. M. M. Kessels, *Appl. Phys. Lett.* **2010**, *960*, 112101.

- [22] D. K. Simon, P. M. Jordan, T. Mikolajick, I. Dirnstorfer, ACS Appl. Mater. Interfaces 2015, 70, 28215.

- [23] M. Garin, J. Heinonen, L. Werner, T. P. Pasanen, V. Vähänissi, A. Haarahiltunen, M. A. Juntunen, H. Savin, *Phys. Rev. Lett.* 2020, 1250, 117702.

- [24] E. Grusell, S. Berg, L. P. Andersson, J. Electrochem. Soc. 1980, 1270, 1573.

- [25] L. P. Andersson, A. O. Evwaraye, Vacuum 1978, 280, 5.

- [26] O. Paz, F. D. Auret, J. F. White, J. Electrochem. Soc. 1984, 1310, 1712.

- [27] F. Volpi, A. R. Peaker, I. Berbezier, A. Ronda, J. Appl. Phys. 2004, 950, 4752.

- [28] F. D. Auret, P. M. Mooney, J. Appl. Phys. 1984, 550, 988.

- [29] B. El-Kareh, A. F. Puttlitz, J. Vac. Sci. Technol. 1978, 150, 1047.

- [30] K. F. Galloway, S. Mayo, Solid State Technol. 1979, 22, 96.

- [31] D. V. Lang, J. Appl. Phys. 1974, 450, 3023.

- [32] K. A. Collett, R. S. Bonilla, P. Hamer, G. Bourret-Sicotte, R. Lobo, T. Kho, P. R. Wilshaw, Sol. Energy Mater. Sol. Cells 2017, 173, 50.

- [33] K. A. Collett, M. Cyrson, R. S. B. Osorio, P. R. Wilshaw, in European Photovoltaic Solar Energy Conf. and Exhibition 2016.

- [34] B. E. Deal, Silicon Dev. Process. Proc. 1969, 13, 36.

- [35] W. D. Eades, Ph.D. Thesis, Stanford University, 1985.

- [36] O. E. Setälä, T. P. Pasanen, J. Ott, V. Vähänissi, H. Savin, *Phys. Status Solidi A* 2021, 2180, 2100214.

- [37] A. C. Diebold, in Handbook of Silicon Semiconductor Metrology, CRC Press, Boca Raton, FL 2001.

- [38] L. M. Terman, Solid-State Electron. 1962, 50, 285.

- [39] M. Wilson, J. Lagowski, L. Jastrzebski, A. Savtchouk, V. Faifer, AIP Conf. Proc. 2001, 5500, 220.

- [40] D. K. Schroder, Mater. Sci. Eng. B 2002, 91, 196.

- [41] A. M. Hoff, D. K. DeBusk, R. W. Schanzer, in *In-Line Methods and Monitors for Process and Yield Improvement*, Vol 3884, International Society for Optics and Photonics, Bellingham, WA 1999, pp. 207–215.

- [42] D. K. Schroder, in Semiconductor Material and Device Characterization, John Wiley & Sons, Inc., Hoboken, NJ 2006.

- [43] B. E. Deal, E. L. MacKenna, P. L. Castro, J. Electrochem. Soc. 1969, 1160, 997.

- [44] R. Khosla, D. Schwarz, H. S. Funk, K. Guguieva, J. Schulze, Solid-State Electron. 2021, 185, 108027.

- [45] N. M. Johnson, D. K. Biegelsen, M. D. Moyer, J. Vac. Sci. Technol. 1981, 190, 390.

- [46] G. Seguini, E. Cianci, C. Wiemer, D. Saynova, J. A. M. van Roosmalen, M. Perego, Appl. Phys. Lett. 2013, 102, 131603.

- [47] K.-H. Cho, Y. J. Cho, H. S. Chang, K.-J. Kim, H. E. Song, J. Korean Phys. Soc. 2015, 670, 995.

- [48] I. Ionica, D. Damianos, A. Kaminski, D. Blanc-Pélissier, G. Ghibaudo, S. Cristoloveanu, L. Bastard, A. Bouchard, X. Mescot, M. Gri, M. Lei, B. Larzelere, G. Vitrant, *ECS Trans.* **2020**, *970*, 119.