This is an electronic reprint of the original article. This reprint may differ from the original in pagination and typographic detail.

Ul Haq, Faizan; Östman, Kim B.; Englund, Mikko; Stadius, Kari; Kosunen, Marko; Koli, Kimmo; Ryynänen, Jussi

A common-gate common-source low noise amplifier based RF front end with selective input impedance matching for blocker-resilient receivers

*Published in:* International Journal of Circuit Theory and Applications

DOI: 10.1002/cta.2473

Published: 01/08/2018

Document Version Peer-reviewed accepted author manuscript, also known as Final accepted manuscript or Post-print

Please cite the original version:

Ul Haq, F., Östman, K. B., Englund, M., Stadius, K., Kosunen, M., Koli, K., & Ryynänen, J. (2018). A commongate common-source low noise amplifier based RF front end with selective input impedance matching for blocker-resilient receivers. *International Journal of Circuit Theory and Applications*, *46*(8), 1427-1442. https://doi.org/10.1002/cta.2473

This material is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

# A Common-Gate Common-Source Low Noise Amplifier Based RF Front-End With Selective Input-Impedance Matching for Blocker Resilient Receivers

Faizan Ul haq<sup>\*1</sup> | Kim B Östman<sup>2</sup> | Mikko Englund<sup>1</sup> | Kari Stadius<sup>1</sup> | Marko Kosunen<sup>1</sup> | Kimmo Koli<sup>3</sup> | Jussi Ryynänen<sup>1</sup>

<sup>1</sup>Dept. of Electronics and Nanoengineering, Aalto university, Espoo, Finland

<sup>2</sup>Nordic Semiconductor, Finland

<sup>3</sup>Huawei Technologies Oy Co. Ltd, Finland

#### Correspondence

\*Faizan Ul haq, Dept. of Electronics and Nanoengineering, Aalto university. Maarintie 8, 02150, Espoo, Finland. Email: faizan.ulhaq@aalto.fi

#### Abstract

This paper presents an integrated wideband RF front-end with improved blocker resilience achieved through selective voltage attenuation at both input and output nodes of the low noise amplifier (LNA). The architecture differs from traditional LNA architectures where blockers are only attenuated at LNA output node. The proposed dual attenuation is attained by designing a low intrinsic input impedance common-gate common-source low noise amplifier (CG-CS LNA) with capacitive feedback, together with an N-path filtering load. The capacitive feedback across the LNA ensures that the selective N-path filtering profile at the LNA output is transferred to the LNA input nodes creating a selective input impedance. Consequently, the achieved front-end input impedance is low at blocker frequencies and matched to the source impedance at the desired frequencies, creating the desired voltage attenuation for blockers. Further, a detailed theoretical analysis of proposed architecture is presented which leads to clear design guidelines. Evaluated in a 28nm fully-depleted silicon-on-insulator CMOS process, front-end is designed for wideband operation from 0.7 to 2.7 GHz. It consumes 11mA current from a 1V supply (excluding LO buffering) and possess a maximum NF of 5.1dB. The front-end demonstrates an out-of-band blocker compression point (BCP) of -1.5dBm and out-of-band IIP3 of +14dBm at a 100MHz offset from local oscillator frequency. In comparison to a traditional CG-CS LNA based front-end with wideband input impedance matching, the proposed front-end achieves 3.5dB improvement in the BCP at a 100MHz offset from LO.

#### **KEYWORDS:**

Blocker tolerance, Selective impedance matching, Low noise amplifier, RF front-end

# **1** | INTRODUCTION

Wireless receivers for emerging radio access standards such as 5G and LTE-A should ideally be able to operate on multiple frequency bands across a wireless spectrum of several GHz. Inherently, such wideband operation allows high power out-of-band (OB) blocker signals at the input of receiver front-end, which can potentially saturate the system.

<sup>&</sup>lt;sup>0</sup>Abbreviations: Blocker tolerance, Selective impedance matching, Low noise amplifier, RF front-end

Traditionally, these OB blockers have mainly been attenuated through high-Q external off-chip RF filtering. However, since external RF filters are mostly non-tunable, multiple RF front-end filters are required to cover a broad range of frequency bands in wideband RF receivers. This creates a practical challenge to design both compact and wideband receivers. To provide a compact on-chip alternative to external off-chip filtering, techniques such as applying N-path filtering at the LNA output nodes (1, 2, 3, 4, 5, 6) and low noise transconductance amplifier (LNTA) based designs (7, 8, 9, 10) have been presented. However, as will be explained later, both of the above techniques generally implement blocker filtering at the LNA/LNTA output nodes, neglecting the filtering requirement at the LNA/LNTA input. Assuming that the blocker voltage gain to the LNA/LNTA output node is quite low, blockers can reach the front-end input swing range limits before the output swing limits. Therefore an optimum design should filter the OB blockers both at input and output nodes of RF front-end.

One can directly implement N-path filtering at LNA input but this results in increased NF due to added N-path mixers directly connected to LNA input (11). To avoid this noise penalty, N-path filters can be implemented in feedback configuration as in (12, 13, 14). In (12), an active interferer reflecting feedback loop is employed while in (13, 14), miller compensated bandpass filters, in dual negative feedback configuration, are utilized to create blocker rejection at LNA input. An active feedback technique has the disadvantage that feedback path may saturate in presence of large blocker while the dual negative feedback together with miller compensated bandpass filters in (13, 14) requires complicated dual feedback architecture for achieving the same goal. In this paper, we propose a blocker resilient RF front-end with low intrinsic input impedance at the blocker frequencies. The proposed circuit offers following key advantages over previously implemented approaches: First, the feedback path is completely passive in nature, reducing chances for feedback path saturation in presence of large blockers. Second, there are no mixers in the feedback path, reducing additional noise and LO power consumption and simplifying the feedback design and third, the proposed design is frequency agnostic meaning no prior information of blocker frequency is required for rejection.

The proposed front-end consists of a low intrinsic input impedance capacitive feedback common-gate (CG) common-source (CS) low-noise-amplifier (LNA) together with an N-path filtering load. The selective N-path filtering response at the LNA output node not only attenuates the blockers at the LNA output but also shapes the LNA input impedance response through the capacitive feedback. The shaped input impedance profile provides a low input impedance at blocker frequencies and a matched input impedance at the desired frequencies, thereby, creating additional blocker voltage attenuation at the LNA input node. In comparison to a traditional RF front based on a CG-CS LNA amplifier with wideband input impedance matching, the proposed front-end achieves +3.5dB improvement in blocker compression point (BCP) at a 100MHz offset from the LO frequency.

In our previous work (11) we have also investigated the possibility of dual node attenuation wideband RF front-end targeted for direct delta sigma receivers (DDSR's). The previously implemented RF front-end employs a global positive feedback from receiver output and an LNTA structure to attain the desired attenuation. However, there is an increased risk of instability in previous solution due to global positive feedback. Further, the solution also requires additional mixers for the feedback up conversion thereby increasing LO power consumption. In comparison, the solution proposed in this paper employs a completely different architecture to achieve the dual node attenuation using a local negative feedback LNA. This allows more sturdy operation with regards to stability.

The paper is organized as follows. Section 2 describes the prior art related to blocker tolerant RF front-ends. Sections 3 and 4 present the traditional capacitive feedback CG LNA, followed by the proposed CG-CS front-end design. Section 5 offers the necessary analysis, and based on the derived equations, design guidelines for CG-CS LNA are presented in Section 6. Section 7 details the circuit design of the CG-CS LNA and presents simulation results.

#### 2 | PRIOR ART: BLOCKER TOLERANT RF FRONT-ENDS

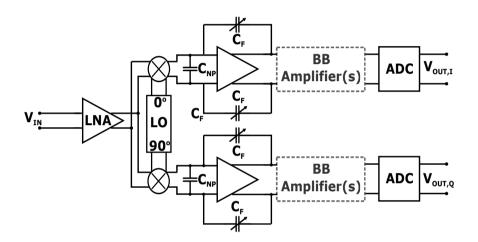

As pointed out in Section I, well-known techniques such as applying N-path filtering to improve RF front-end OB blocker attenuation have been demonstrated previously (1, 2, 3, 4, 5, 6). N-path filtering as an on-chip solution provides accurately controlled high-Q RF bandpass filtering. Figure 1 shows a typical N-path filter based down-conversion receiver. The N-path capacitor  $C_{NP}$  together with feedback capacitor  $C_F$  and mixer switch resistance  $R_{SW}$  form a low pass filter at the mixer-tobaseband (BB) interface. Because a passive mixer is transparent in nature, it converts the BB low pass filtering response to an RF bandpass response. The advantage of the N-path filtering technique lies in its ease of tunability. The bandpass response can be easily tuned to the desired frequency by changing the local-oscillator (LO) frequency of the passive mixers. Further, if a higher order BB impedance is used as the N-path load, one can create a higher order bandpass response at the RF nodes(8). This helps to create additional attenuation for blocker frequencies. However, N-path filters do have some practical limitations. In contrast to off-chip bandpass filters, blocker attenuation in N-path filters is limited by the mixer switch resistance  $R_{SW}$  and the LNA transconductance  $g_{mLNA}$  (2). This is due to the fact that at blocker frequencies, the N-path filtering capacitors provide minimum impedance, consequently making the N-path filter input impedance approximately equal to  $R_{SW}$ . This defines the approximate blocker gain as  $g_{mLNA}$  times  $R_{SW}$ . Consequently, both of these values should be be minimized for reduced blocker gain. However, these parameters cannot be reduced indefinitely due to limitations on LO drive power consumption and LNA noise contribution.

Another technique for OB blocker rejection is to avoid voltage gain at RF frequencies by employing low-noise-transconductance-amplifier (LNTA)(7, 8, 9, 10). Receivers employing a LNTA's shift almost all the gain to the baseband (BB) stages, where it is easier to implement selective on-chip filtering for suppressing OB blockers. Reduced gain at RF frequencies results in a more linear RF-front end.

However, LNTA based receivers and N-path filtering techniques both generally implement filtering only at the output of the LNA/LNTA, neglecting the filtering opportunity at the LNA/LNTA input. Without filtering at input node and provided the low blocker gain from the LNA/LNTA, the LNA/LNTA transconductor input swing range may be reached before that of its output.

FIGURE 1 Generic block diagram of a direct conversion receiver with N-path filtering .

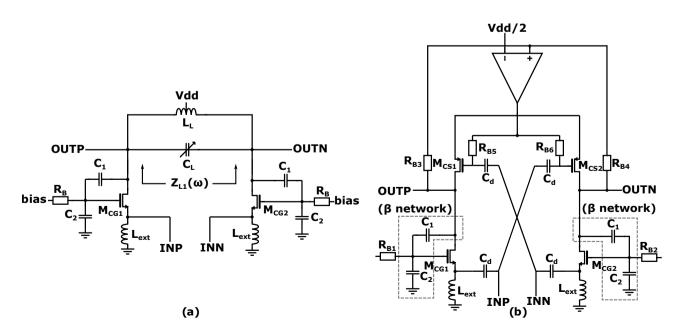

FIGURE 2 (a) Capacitive feedback CG LNA and (b) Proposed CG-CS LNA for blocker resilient RF front-ends.

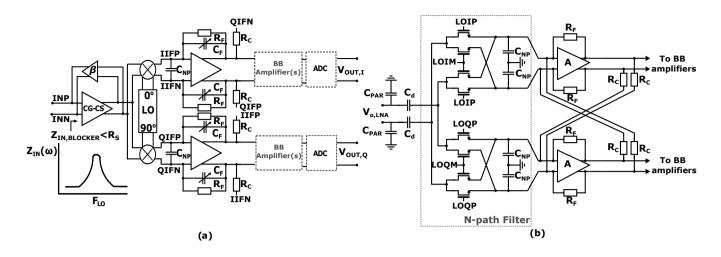

**FIGURE 3** (a) Block diagram of the proposed RF front-end. (b) Differential implementation of a quadrature N-path filter load with complex BB feedback for frequency offset tuning.

This can cause the transconductor to enter into non-linear operation. Therefore, an optimum design should ideally filter the OB blockers already at the LNA/LNTA input.

Based on the aforementioned discussion, our solution is based on a low intrinsic input impedance capacitive feedback CG-CS LNA together with N-path filtering. The selective N-path response at the LNA output shapes the LNA input impedance profile, thereby creating blocker voltage attenuation at both the LNA input and output nodes.

# 3 | CAPACITIVE FEEDBACK CG LNA

Figure 2 (a) presents the capacitive feedback CG LNA with a selective input impedance profile, implemented in (15, 16) for an LC load. It demonstrates a narrowband input impedance profile when it is loaded by a selective impedance such as an LC resonant tank. The input impedance  $Z_{IN}$  of the LNA is given as (15):

$$Z_{IN} = \frac{1}{gm_1} + (\frac{C_1}{C_1 + C_2}) Z_{L1}(\omega), \tag{1}$$

where  $gm_1$  is the transconductance of the device  $M_{CG1-2}$  and  $Z_{L1}(\omega)$  represents the LNA load impedance at the frequency  $\omega$ . From Eq. 1, one can infer the following: At OB blocker frequencies, where  $Z_{L1}(\omega)$  is quite small,  $Z_{IN}$  is approximately equal to  $1/gm_1$ . This means that  $Z_{IN} < R_S$  can be achieved by controlling the value of  $gm_1$ . This will ensure attenuation for blockers at LNA input. At the desired frequency, however, the input impedance can be tuned to matched condition by controlling the resonant frequency of the load impedance  $Z_{L1}(\omega)$  and the feedback factor  $\beta$  given by:

$$\beta = \frac{C_1}{C_1 + C_2}.$$

(2)

However, in reality, power consumption constraints of a practical design limit the designer to implement a very high value of CG gm. Therefore, in practice, blocker attenuation at LNA input due to lower LNA impedance is a compromise between input large signal linearity and power consumption. This compromise holds true for our next presented capacitive feedback CG-CS LNA as well.

## 4 | PROPOSED BLOCKER TOLERANT RF FRONT-END

### 4.1 | Capacitive Feedback CG-CS LNA

The LNA's in (15) and (16) both implement switchable LC loads to tune different frequency bands. In a wideband receiver scenario, switchable integrated LC loads consume huge silicon area while providing only a limited frequency tunability, and are therefore not a viable solution. Our proposed solution instead implements this wideband tunability through application of on-chip N-path filtering as LNA load. As per the authors knowledge this is the first paper where a capacitive feedback LNA has been implemented together with N-path filtering.

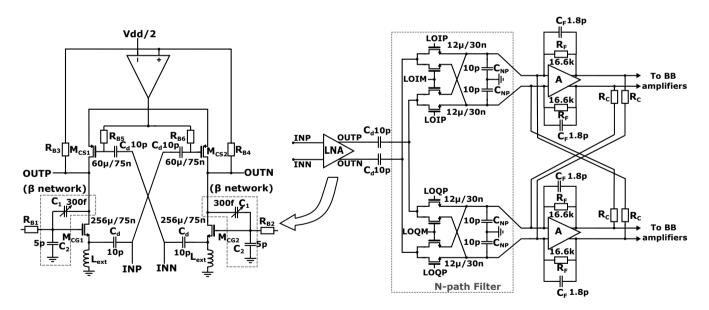

Figure 2 (b) presents the detailed diagram of the capacitive feedback CG-CS LNA while Figure 3 (a) presents the proposed blocker resilient CG-CS LNA based RF front-end. The LNA consists of push-pull CG and CS amplifiers where the capacitive feedback CG stage works in the same way as a typical capacitive feedback CG amplifier. A CS stage is added to increase the output impedance of the LNA as compared to resistive loads. This high output impedance is required for proper functioning of the N-path filtering as it affects the relative blocker attenuation (17). Furthermore, it also increases the LNA gain and provides flexibility to tune the LNA gain when needed. Resistors  $R_{B1}$  and  $R_{B2}$  provide the necessary dc-biasing while resistors  $R_{B3}$ - $R_{B6}$  are added to sense the dc-bias voltage for the common mode feedback loop. The designed common-mode feedback loop ensures that the output common-mode voltage at OUTP/OUTN is set at half of the supply voltage, which creates an optimum output swing range.

#### 4.2 | N-path Filter load

Figure 3 (b) presents the designed quadrature passive mixer N-path load. It consists of two quadrature passive mixers switching at an LO of 25% duty cycle. This creates a total of four switching phases. The number of N-path phases may vary depending on different N-path implementations. 8-phase and 16-phase arrangements have been reported in (18, 19). Additional N-path phases provide higher harmonic rejection and selectivity but come at the cost of increased complexity. In this paper, we have therefore restricted ourselves to a 4-phase implementation.

The N-path filter is loaded with a baseband impedance, which is a parallel combination of N-path capacitor  $C_{NP}$  (impedance  $Z_{C,NP}$ ) and the BB amplifier input impedance  $Z_{BB}$ . The capacitors  $C_{NP}$  and  $C_F$  (multiplied by gain due to miller effect) form the total capacitance of N-path filter. They together with quadrature passive mixers constitute a first order band-pass response as seen from the RF side of mixers. Nevertheless, it is possible to implement higher order N-path baseband impedances such as in (8) with proposed LNA. Further, the baseband stages input impedance  $Z_{BB}$  is implemented through a feedback resistor  $R_F$  such that  $Z_{BB} \approx R_F/(1 + A)$ . Here A is the open loop gain of the feedback amplifier.

Complex feedback resistors  $R_C$  are added to compensate the effect of any parasitic capacitance at the LNA output. Any complex impedance present at the LNA output will manifest itself as a bandpass filter response offset from LO. This shifts the maximum gain of the LNA away from the LO and results in non-optimal front-end performance(20). The complex feedback resistors  $R_C$  overcome this problem by providing a complex BB input impedance(18, 21, 22).

Next we will derive the voltage gain, input impedance and NF expressions for the proposed front-end design. Unless otherwise specified, all circuit parameters in the derived expressions will be single-ended values.

#### 5 | THEORETICAL ANALYSIS

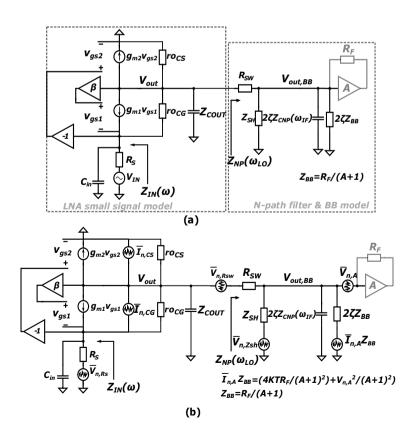

For the derivation of desired design equations a simplified small signal model of proposed circuit can be made as shown in Figure 4 (a). In the model,  $R_S$  represents input source impedance,  $C_{in}$  is the parasitic capacitance at input nodes,  $gm_1$  and  $ro_{CG}$  represent the CG amplifier transconductance and output impedance while  $gm_2$  and  $ro_{CS}$  represent the CS amplifiers transconductance and output impedance by capacitors  $C_1$  and  $C_2$  is represented through a feedback factor  $\beta$ . This assumption ignores the high frequency currents flowing through the capacitors  $C_1$  and  $C_2$ . Nevertheless, this effect of high frequency current can be included in the model as a current flowing through an equivalent capacitance of  $C_1C_2/(C_1 + C_2)$  and can be lumped in the output capacitance  $C_{out}=C_1C_2/(C_1+C_2)+C_{par}$ , where  $C_{par}$  is the parasitic capacitance at LNA output nodes. The LNA is loaded with an impedance  $Z_L$ , which can be represented as a parallel combination of N-path filter input impedance  $Z_{NP}(\omega_{LO})$ ,  $C_{out}$  impedance ( $Z_{COUT}$ ) and  $ro_{CS}$ .

In the N-path filter model,  $R_{SW}$  represents mixer switch resistance,  $Z_{BB}(\omega_{IF})$  is the BB amplifier input impedance at intermediate frequency (IF),  $Z_{CNP}(\omega_{IF})$  is the impedance of the N-path capacitor at intermediate frequency (IF) and  $\zeta$  represents the frequency scaling factor. For four-phase quadrature passive mixers with 25% duty cycle,  $\zeta = 2/\pi^2$ . Further,  $Z_{SH}(\omega_{LO})$  is virtual shunt impedance representing the power dissipation due to baseband signal upconversion. It can be expressed as(18):

$$Z_{SH} = \left(\sum_{n=3,7,11..}^{\infty} \frac{1}{n^2 Z_{OLNA}^*(nf_{LO})} + \sum_{n=50,13}^{\infty} \frac{1}{n^2 Z_{OLNA}(nf_{LO})}\right)^{-1}$$

(3)

Here, Z<sub>OLNA</sub>(nf<sub>LO</sub>) represents the LNA output impedance at specified nth harmonic of LO frequency.

As we will demonstrate later, the presented model is able to follow the transistor level design with reasonable accuracy. However, one limitation for the simplified small signal model originates from the complex nature of upconverted N-path response. Any complex impedance present at the LNA output will manifest itself as a bandpass filter response offset from the LO, shifting the maximum gain of the LNA away from LO. A slight change in gain will also be observed (20). The analytical equations do not take this complex frequency shift effect in account. This was done to avoid overwhelming complexity in derived equations and to make intuitive sense from results. Consequently, a small deviation from simulated results is expected. Nevertheless, as we will demonstrate in upcoming section, the deviation is small as long as capacitor  $C_1$  is kept to lower values.

FIGURE 4 (a) Small signal model of the proposed front-end with N-path filter load and (b) its noise model.

# 5.1 | Voltage Gain

The RF voltage Gain  $(A_{vRF})$  of the proposed LNA can be calculated using the small signal model shown in Figure 4 (a) and is given by:

$$A_{vRF} = \frac{2Z_L(\omega)[1 + ro_{CG}(gm_1 + gm_2)]}{\kappa},\tag{4}$$

$\kappa = R_{S} + Z_{L} + ro_{CG} + R_{S}(ro_{CG}gm_{1} - Z_{L}gm_{2}) + Z_{L}ro_{CG}\beta gm_{1}(1 - R_{S}gm_{2}) + sC_{in}(R_{S}Z_{L} + R_{S}ro_{CG} + R_{S}Z_{L}ro_{CG}\beta gm_{1}),$ (5)

and

$$\beta = \frac{C_1 + C_{GD,CG}}{C_1 + C_{GD,CG} + C_2}.$$

(6)

Here  $C_{GD,CG}$  is the gate-to-drain capacitance of the CG transistor and  $Z_L(\omega)$  is the parallel combination of N-path filter input impedance  $Z_{NP}(\omega_{LO})$ ,  $C_{out}$  impedance  $(Z_{COUT})$  and  $ro_{CS}$ .  $Z_{NP}(\omega_{LO})$  can be given by (20):

$$Z_{NP}(\omega) = R_{SW} + 2\zeta Z_{BB}(\omega_{IF}) ||Z_{SH}(\omega_{LO})|| 2\zeta Z_{CNP}(\omega_{IF}).$$

<sup>(7)</sup>

The total capacitance of N-path filter  $C_{NP}$  required to achieve certain BB bandwidth can be derived as:

$$C_{NP} \approx \frac{2\zeta [1 + (Z_{OLNA} + R_{SW})](1/Z_{SH} + 1/2\zeta Z_{BB})}{2\pi f_{BW}(Z_{OLNA} + R_{SW})}$$

(8)

The derived voltage gain Eq.4 is quite complex to offer intuitive understanding for the proposed circuit. We therefore, simplify the Eq.4 by neglecting the parasitic capacitances and CG/CS amplifier output impedances. This simplification results in further deviation from transistor level simulation results. Nevertheless, it allows us to crudely establish circuit behavior in terms of main design parameters. The simplified form of Eq.4 can be given as:

$$A_{vRF} = \frac{2(gm_1 + gm_2)Z_L(\omega)}{1 + gm_1[\beta Z_L(\omega) + R_S - gm_2\beta R_S Z_L(\omega)]}$$

(9)

Eq. 9 suggests that gain can be controlled mainly with  $gm_1, gm_2, \beta$  and  $Z_L$ . As we will demonstrate later, first three of these parameters directly influence the noise and input impedance-profile of LNA and therefore, should be chosen to meet the required noise levels and input impedance profile. This leaves us with  $Z_L$  to control LNA gain which is inherently a bandpass response due to  $Z_{CNP}(\omega)$ . At the desired frequencies,  $Z_{CNP}(\omega)$  in  $Z_L$  behaves as a very high impedance and therefore can be neglected. This means that  $Z_L$  can be controlled through  $Z_{BB}(\omega_{IF})$  to achieve the desired gain. In contrast, at the far-away blocker frequencies, the  $Z_{CNP}(\omega)$  behaves as nearly short-circuit causing  $Z_L$  to approach  $R_{SW}$  impedance. This means that if  $R_{SW}$  is kept small, the gain at blocker frequencies can be reduced to a much lower value as desired.

RF-to-BB voltage gain of the proposed front-end can be found as:

$$A_{vBB} = A_{vRF} \left(\frac{\pi}{2\sqrt{2}}\right) \left(\frac{Z_{BBtot}}{Z_{BBtot} + R_{SW}}\right),\tag{10}$$

where

$$Z_{BBtot} = 2\zeta Z_{BB}(\omega_{IF}) || Z_{SH}(\omega_{LO}) || 2\zeta Z_{NP}(\omega_{IF}).$$

<sup>(11)</sup>

and the factor  $\frac{\pi}{2\sqrt{2}}$  comes from the Fourier series analysis of a quadrature downconversion mixer with 25% dutycycle.

# 5.2 | Input Impedance

Based on the proposed front-end small signal model, presented in Figure 4 , the input impedance (Z<sub>IN</sub>) can be derived as:

$$Z_{IN} = \frac{Z_L + ro_{CG} + Z_L ro_{CG}\beta gm_1}{1 + ro_{CG}gm_1 - Z_L gm_2 - Z_L ro_{CG}gm_1 gm_2\beta + sC_{in}[Z_L + ro_{CG} + Z_L ro_{CG}\beta gm_1]},$$

(12)

To provide an intuitive understanding, Eq.12 can be simplified by neglecting the effect of parasitic capacitances and CG/CS amplifier output impedances. Though this simplification results in further deviation from transistor level simulation results, it allows us to crudely establish circuit behavior in terms of main design parameters. The simplified form of Eq.12 can be given as:

$$Z_{IN} = \frac{1}{gm_1(1 - \beta gm_2 Z_L(\omega))} + \frac{\beta Z_L(\omega)}{1 - \beta gm_2 Z_L(\omega)}$$

(13)

Similar to an LC load, the  $Z_L(\omega)$  load created by N-path filtering presents a bandpass filter response at RF, i.e, high impedance at the desired frequency and low impedance at blocker frequencies. Consequently, Eq. 15 suggests that at blocker frequencies, contribution of  $Z_L(\omega)$  to the input impedance  $Z_{IN}$  is minimal and  $Z_{IN}$  is roughly equal to  $1/gm_1$ . To create a selective input impedance profile, a high value of  $gm_1$  is selected such that the input impedance at blocker frequencies is much lower than the source impedance  $R_S$ . On the other hand, at the desired frequency, higher  $Z_L(\omega)$  increases the  $Z_{IN}$  beyond  $1/gm_1$  but can be tuned to matched condition by proper selection of feedback factor  $\beta$ .

#### 5.3 | Noise Figure

For the proposed architecture, a noise model constituting all major noise sources can be constructed as shown in Figure 4 b). For the LNA, main noise contribution comes from the channel currents of CG and CS devices while in the N-path filter load, the main noise contributors are the  $R_{SW}$  thermal noise and the noise produced by  $Z_{SH}$ . Through a simplified nodal analysis, we can derive the noise factor *F* of proposed front-end as:

$$F = 1 + \left(\frac{4Z_{L}(\omega)^{2}\gamma gm_{1}}{A_{\nu RF}^{2}R_{S}}\right)\left(\frac{ro_{CG} - R_{S}ro_{CG}gm_{2} + sC_{in}R_{S}ro_{CG}}{\alpha}\right)^{2} + \left(\frac{4Z_{L}(\omega)^{2}\gamma gm_{2}}{A_{\nu RF}^{2}R_{S}}\right)\left(\frac{R_{S} + ro_{CG} + R_{S}ro_{CG}gm_{1} + sC_{in}R_{S}ro_{CG}}{\alpha}\right)^{2} + \left(\frac{V_{NP}^{2}(R_{OLNA}/(R_{OLNA} + Z_{L}))^{2}}{KTR_{S}A_{\nu RF}^{2}}\right),$$

(14)

where

$$\alpha = R_{S} + Z_{L} + ro_{CG} - R_{S}Z_{L}gm_{2} + ro_{CG}gm_{1}(R_{S} + Z_{L}\beta) - R_{S}Z_{L}ro_{CG}\beta gm_{1}gm_{2} + sC_{in}[R_{S}Z_{L} + R_{S}ro_{CG} + R_{S}Z_{L}ro_{CG}\beta gm_{1}],$$

(15)

and LNA output resistance is given as:

$$R_{OLNA} = \frac{r_{oCS}(R_S + r_{oCG} + R_S r_{oCG} gm_1)}{R_S + r_{oCG}(1 + gm_1 R_S) + r_{oCS}(1 - gm_2 R_S) + r_{oCG} r_{oCS} \beta gm_1(1 - gm_2 R_S)},$$

(16)

In Eq. 14, the second and third terms in the NF expression account for the noise contributions from the CG and CS devices respectively, while the last term shows the contribution of the N-path filter and the upconverted noise from BB stages. In the NF expression, factor  $\gamma$  accounts for a constant MOSFET noise parameter whose value is derived to be 2/3 for long channel devices. Recent submicron processes tend to exhibit higher values. Av' and  $\overline{V_{NP}^2}$  are respectively the loaded voltage gain and the input referred noise of the N-path filter and BB stages at  $\omega_{IF}$ .  $\overline{V_{NP}^2}$  can be derived from (17),(18) as:

$$V_{NP}^2 = 4KTR_{SW} |\rho(Z_{SH}2\zeta Z_{BB})|^2 +$$

$$4KTRe(Z_{SH})(|\rho 2\zeta Z_{BB}(R_{SW} + Z_{OLNA})|)^{2} + 4KTR_{F}(|\rho \frac{Z_{SH}(R_{SW} + Z_{OLNA})}{1 + A_{BB}}|\frac{2\sqrt{2}}{\pi})^{2} + (|\rho \frac{Z_{SH}(R_{SW} + Z_{OLNA})}{1 + A_{BB}}|\frac{2\sqrt{2}}{\pi})^{2}\overline{V_{N,amp}^{2}} + (|2\rho\zeta Z_{BB}(R_{SW} + Z_{OLNA} + Z_{SH})|\frac{2\sqrt{2}}{\pi})^{2}\overline{V_{N,amp}^{2}},$$

(17)

where

$$\rho = \frac{(Z_{BBtot} + R_{SW})/Z_{BBtot}}{(R_{SW} + Z_{OLNA})(2\zeta Z_{BB} + Z_{SH}) + Z_{SH}2\zeta Z_{BB}}),$$

(18)

and  $V_{N,amp}^2$  is the input referred noised of the BB amplifier,  $A_{BB}$  is the open loop voltage gain of the BB integrator and  $R_F$  is the feedback resistor across the BB integrator such that:

$$Z_{BB} = \frac{R_F}{1 + A_{BB}}.$$

(19)

The first term of Eq. 17 corresponds to the noise contribution from  $R_{SW}$ , the second term to the noise contribution of  $Z_{SH}$ , the third term to the noise contribution of  $R_F$ , and finally the fourth and fifth terms correspond to the noise contribution from the BB amplifier. As can be observed from Eq.17, the noise contribution from the baseband amplifiers  $\overline{V_{N,amp}}$  and  $R_F$  is divided by the gain of LNA and therefore has a reduced effect in overall  $\overline{V_{NP}}$  value. This leaves  $R_{SW}$  and  $Z_{SH}$  as main noise contributors in overall  $\overline{V_{NP}}$ . There values however, can not be changed arbitrarily due to LO driver and LNA power consumption constraints.

One can simplify the NF Eq. 14 by neglecting the effect of parasitic capacitances and CG/CS output impedances. The simplified equation can be given as:

$$F = 1 + \left(\frac{Z_L(\omega)^2 \gamma g m_1}{A \nu'^2 R_S}\right) \left(\frac{1 - g m_2 R_S}{\alpha}\right)^2$$

+

$$(\frac{Z_L(\omega)^2 \gamma g m_2}{A \upsilon'^2 R_S})(\frac{1+g m_1 R_S}{\alpha})^2 + (\frac{V_{NP}^2}{4KTR_S A \upsilon'^2})(\frac{1+g m_1 R_S}{\alpha})^2,$$

(20)

where

$$\alpha = 1 + gm_1(R_S + Z_L\beta - Z_L(\omega)R_S\beta gm_2)$$

<sup>(21)</sup>

However, even the simplified form of Eq. 14 offers little intuition about design trade-offs of proposed circuit. Therefore, in the upcoming Section 7, we will utilize the derived equations to constitute a graphical approach for intuitively explaining the design trade-offs.

#### 5.4 | Analysis Validation

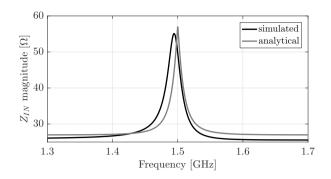

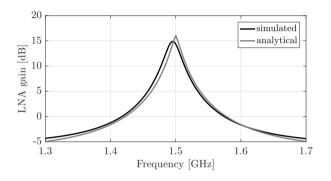

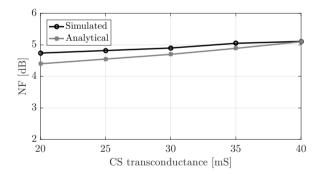

To confirm the analytical results in equations 4-21, we designed a transistor level CG-CS LNA based front-end in a 28nm FDSOI CMOS technology, with the following practical values:  $gm_1 = 80mS$ ,  $gm_2 = 30mS$ ,  $ro_{CG}=900\Omega$ ,  $ro_{CS}=1600\Omega$ ,  $R_{SW} = 10\Omega$ ,  $C_{NP} = 10pF$ ,  $C_F = 1.8pF$ ,  $C_1 = 300fF$ ,  $C_2 = 5pF$ ,  $R_F = 16.6k\Omega$ ,  $C_{in} = 300fF$ ,  $C_{GD,CG} = 100fF$ ,  $C_{out} = C_{out,par} + (C_1+C_{GD,CG})C_2/(C_1+C_{GD,CG}+C_2) = 370+100 = 470fF$ ,  $V_{NP}^2 = 5 \times 10^{-18}V^2/Hz$ ,  $\gamma = 1.1$  and an ideal BB amplifier with open loop voltage gain of 25dB. The values of  $gm_1$ ,  $gm_2$ ,  $R_{SW}$ ,  $C_{NP}$ ,  $C_F$ ,  $C_1$ ,  $C_2$  and  $R_F$  were chosen while keeping in mind their practically implementable range and design targets(as explained in Section 7) for proposed design while  $ro_{CG}$ ,  $ro_{CS}$ ,  $C_{in}$ ,  $C_{out}$ ,  $C_{GD,CG}$ ,  $V_{NP}^2$  and  $\gamma$  are the estimated values based on transistor modeling in the used FDSOI process. Later in Section 7, frontend will be designed with above design parameters. Results for the LNA input impedance and voltage gain are plotted in Figures 5 and 6 , respectively. As can be seen, the analytical and simulated results match quite closely. The small difference in the simulated and analytical results can be attributed to a complex LNA output impedance caused by  $C_{out}$ . Any complex impedance present at the LNA output will manifest itself as a bandpass filter response offset from the LO, shifting the maximum gain of the LNA away from LO(20). To avoid overwhelming complexity in derived equations and to make intuitive sense from results,

FIGURE 5 Comparison between calculated and simulated input impedance.

FIGURE 6 Comparison between calculated and simulated LNA gain.

FIGURE 7 Comparison between calculated and simulated NF.

the analytical equations do not take this complex frequency shift effect in account. Therefore, a small deviation from simulated results is expected. For the quantitative noise analysis, we compare the NF results from Eq. 14 with transistor-level front-end simulations. Figure 7 presents the simulated and calculated NF versus CS transconductance  $gm_2$ . It can be seen that the NF is high for higher values of  $gm_2$ . This dependence of NF on  $gm_2$  will be further elaborated in following section.

# 6 | DESIGN GUIDELINES

The design targets for the proposed front-end are to provide high blocker resilience through improved large signal linearity and dual node blocker voltage attenuation, with acceptable NF and input matching. In this section we examine the proposed front-end to obtain optimum circuit parameter values such as  $gm_1$ ,  $gm_2$ ,  $\beta$  and  $Z_L$ , meeting the design requirements.

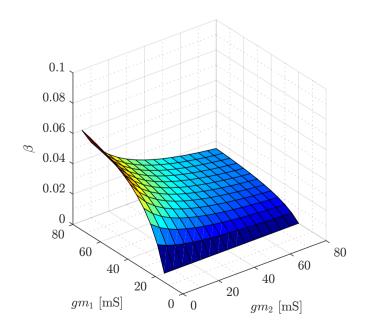

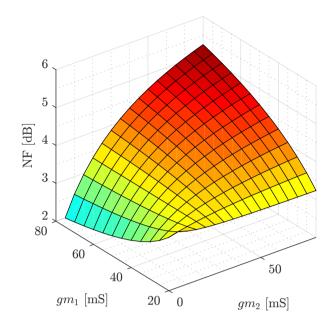

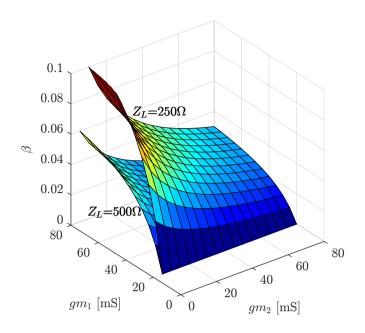

We begin by assuming a fixed load impedance of  $Z_L = 500\Omega$ . This is done to simplify the analysis by reducing additional variables. Later, we will demonstrate how  $Z_L$  affects the overall front-end response. With the selected value of  $Z_L$ , first, we use Eq. 13 to plot the required feedback factor  $\beta$  for an ideal input match, against different values of gm<sub>1</sub> and gm<sub>2</sub>. The derived  $\beta$  values are plotted in Figure 8 . These derived values are then used to calculate the LNA NF in impedance-matched conditions, using Eq. 21. We assume that  $\overline{V_{NP}^2} = 5 \times 10^{-18} V^2 / Hz$  and  $\gamma = 1.1$  for the analysis. The resulting NF is plotted for different values of gm<sub>1</sub> and gm<sub>2</sub> in Figure 9 .

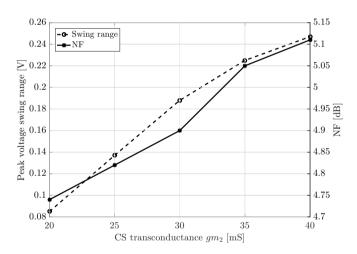

NF results in Figure 9 demonstrate that a smaller value of  $gm_2$  is desired for reduced NF. We can achieve this smaller  $gm_2$  value by having a smaller aspect-ratio for CS device. However, too small aspect-ratio for the CS device in comparison to the CG reduces the LNA linear output swing range, and consequently lowers the large signal linearity. This is depicted in Figure 10, where the transistor-level simulation results for NF and maximum peak output voltage swing range are plotted against CS transconductance  $gm_2$ . As expected, a smaller  $gm_2$  leads to reduced NF and output peak voltage swing range. The decrease in output swing range can be attributed to a higher saturation voltage ( $V_{DSAT}$ ) of the CS devices. Consequently,  $gm_2$  cannot be reduced significantly in comparison to  $gm_1$ , without significantly affecting the larger signal linearity of LNA. The choice of  $gm_2$  is thus a trade-off between NF and large signal linearity.

In the next step, we examine the effect of  $Z_L(\omega)$  on the front-end performance. In Figure 11 , we plot the required value of  $\beta$  for input matching at two different values of  $Z_L(\omega)$  values. It can be observed that for higher values of  $Z_L(\omega)$ , one needs a lower  $\beta$  to achieve input matching. After a certain limit, designing the LNA for lower values of  $\beta$  becomes impractical due to very small values of  $C_1$ . Once  $C_1$  approaches closer to the CG gate-to-drain parasitic capacitance  $C_{GD}$ , the effect of  $C_{GD}$  is significant and therefore needs to be considered in the effective feedback factor  $\beta$ . Therefore, we propose designing the CG-CS LNA for moderately lower values of  $Z_L(\omega_0)$ .

In conclusion, based on the above reasoning, we propose designing of capacitive feedback CG-CS amplifier with  $gm_2 < gm_1$  and a moderately low value of  $Z_{I}(\omega)$  to ensure practical values for  $C_1$ .

# 7 | PERFORMANCE EVALUATION

Based on the design guidelines in Section 6, we selected  $gm_1 = 80mS$  and a lower  $gm_2 = 30mS$  for LNA design. Selection of  $gm_2 < gm_1$  is a compromise between large-signal linearity and NF. Detailed diagram of designed circuit is shown in Figure

**FIGURE 8** Required feedback factor  $\beta$ , for  $Z_{IN} = 50\Omega$ , for different values of  $gm_1$  and  $gm_2$ .

**FIGURE 9** Theoretical NF, for  $Z_{IN} = 50\Omega$ , for different values of  $gm_1$  and  $gm_2$ .

FIGURE 10 Transistor level simulations for output voltage swing range and NF, versus CS transconductance gm<sub>2</sub>.

12 .To maximize output voltage swing range, the output common mode voltage of the LNA was set to half of the supply voltage by implementing the common-mode feedback loop depicted in Figure 2 . A quadrature passive mixer with a switch resistance  $R_{SW} = 10\Omega$  together with the baseband capacitance  $C_{NP} = 10$ pF and an ideal differential BB amplifier with Miller capacitance  $C_F = 1.8$ pF formed a first order N-path filter. This  $R_{SW} = 10\Omega$  was achieved with transistor width of  $12\mu m$  by the application of proper body-bias in FDSOI process. This reduced the LO buffer sizes and consequently their current consumption to 1mA. The value of feedback resistor  $R_F$  was set to 16.5k $\Omega$  to adjust the front-end voltage gain to 15dB. For Additionally, in order to match the pre-layout simulated response more closely to the real measurements, estimated values of key PCB and layout parasitics, pad capacitances, bondwire inductances and s-parameter models of the off-chip RF chokes ( $L_{ext}$ ) were included in simulations.

The parasitic capacitance associated with the LNA output node can shift the LNA center frequency away from the LO frequency(20). This was corrected by implementing a resistive complex negative feedback from the output node of the baseband differential amplifier, as depicted in Figure 3 (b).

**FIGURE 11** Feedback factor  $\beta$ , at Zin = 50 $\Omega$ , for different values of gm<sub>1</sub> and gm<sub>2</sub>. For higher Z<sub>L</sub>, a lower value of  $\beta$  is required for input matching.

FIGURE 12 Designed circuit for simulations.

The proposed front-end was evaluated in a 28nm fully-depleted silicon-on-insulator (FD-SOI) CMOS process with 1V supply voltage. The front-end is configurable from 0.7-2.7GHz with BB bandwidth of 10MHz and consumes 11.5mA current, excluding LO buffering.

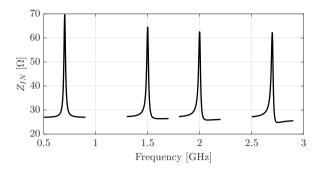

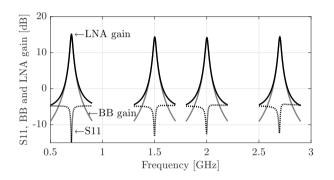

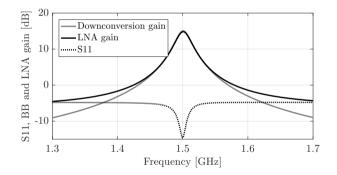

Figure 13 demonstrates the simulated differential  $Z_{IN}$ . As can be seen,  $Z_{IN} \approx 25\Omega$  at blocker frequencies. Assuming an antenna impedance of 100 $\Omega$  (differential), this creates the required blocker voltage attenuation. Additionally, we observe  $Z_{IN} > 25\Omega$  for the upper end of the 0.7-2.7GHz band. At higher frequencies the effect of parasitics changes the effective feedback factor  $\beta$  and causes a change in  $Z_{IN}$ . Figures 14 and 15 show the simulated gain and  $S_{11}$  for the proposed front-end. Gain and

FIGURE 13 Simulated real part of the LNA input impedance  $Z_{IN}$  around  $f_{LO} = 0.7, 1.5, 2, and 2.7$  GHz.

**FIGURE 14** Simulated S<sub>11</sub>, LNA and front-end downconversion gain around  $f_{LO} = 0.7, 1.5, 2, and 2.7$  GHz.

FIGURE 15 Simulated S<sub>11</sub>, LNA and front-end downconversion gain.

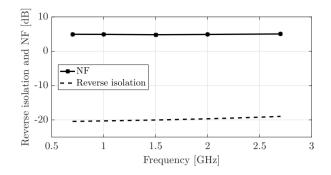

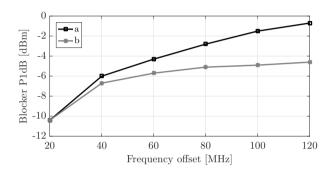

S<sub>11</sub> have been plotted at four operating frequencies in the 0.7-2.7GHz band, demonstrating the desired configurability. Figure 16 presents the front-end NF and LNA reverse isolation across the whole band of 0.7-2.7GHz. A maximum NF of 5.1dB and minimum reverse isolation of -19dB is observed. As explained in the previous sections, there is a compromise between large signal linearity and NF. Therefore, we choose a moderately high value of NF to have better large signal performance. Further, the reverse isolation results demonstrate atleast 19 dB suppression of LO oscillator leakage to antennas compared to mixer-first receivers. Figure 17 presents the front-end blocker 1dB compression point (BCP) when loaded with a first order N-path response. The simulated results demonstrate the blocker tolerance of -1.5dBm at a 100MHz offset from the LO frequency. Further, in order to quantitatively observe the improvement of BCP thanks to the selective input impedance profile, a CG-CS LNA based RF front-end with flat wideband input matching was designed and simulated for same the voltage gain and baseband bandwidth. Its simulated BCP results are plotted in the same Figure 17. The proposed front-end demonstrates 3.5dB improvement in BCP at a 100MHz offset from the LO frequency, thanks to selective input impedance matching.

FIGURE 16 Simulated front-end noise figure and LNA reverse isolation for different operating frequencies.

**FIGURE 17** (a) Simulated out-of-band blocker compression point (BCP) of the proposed RF front-end and (b) BCP for CG-CS LNA based RF front end with wideband input matching. In comparison to (b), the proposed front-end achieves 3.5dB higher BCP at a 100MHz offset from LO.

Table 1 compares the performance of proposed front-end with other relevant front-end structures with blocker rejection at LNA input. As desired, the front-end achieves competitive large signal linearity even with a reduced power supply and lower power consumption with a simplified passive feedback approach.

# 8 | CONCLUSION

Emerging wideband RF-to-digital receivers need to operate in the presence of strong OB blockers. These blockers can cause receiver input amplifiers to saturate and therefore make its operation non-linear. In this paper, we have presented a blocker resilient low intrinsic input impedance RF front-end. The front-end achieves this blocker resilience through blocker attenuation at both front-end input and output nodes. This dual attenuation is achieved through tunable N-path filtering at the CG-CS LNA output nodes, which is in turn reflected back to the LNA input through capacitive feedback. The resulting input impedance of RF front-end is lower at blocker frequencies while being matched at desired frequencies, thereby creating additional blocker attenuation at the RF front-end input. Further, a detailed theoretical analysis of proposed architecture is presented which leads to simplified design guidelines.

The front-end is designed for an operating frequency of 0.7 to 2.7GHz, where desired configurability is achieved by tuning the center frequency of the N-path filter through the LO signal. Evaluated in a 28nm FD-SOI, simulated results demonstrate wideband tunable operation in the operating band with maximum a NF of 5.1dB. The front-end achieves -1.5dBm of input BCP and +14dBm of OB IIP3 at a 100MHz frequency offset from the LO frequency. In comparison to relevant front-end architectures (12, 13, 14), where blocker rejection is performed at LNA input, the proposed front-end offers a simplified and passive feedback path. This reduces the possibility of feedback path saturating in presence of large blockers. When compared to traditional CG-CS LNA amplifier based RF front end with wideband input impedance matching, the proposed front-end achieves 3.5dB improvement in blocker compression point (BCP) at a 100MHz offset from the LO frequency.

# 9 | ACKNOWLEDGEMENTS

This work was supported by the Academy of Finland.

#### References

- Lin Z., Mak P. I., Martins R. P. A 0.028mm2 11mW single-mixing blocker-tolerant receiver with double-RF N-path filtering, S11 centering, +13dBm OB-IIP3 and 1.5-to-2.9dB NF. *IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers*. 2015;:1-3.

- [2] Englund M., Östman K.B., Viitala O., et al. A Programmable 0.7-2.7 GHz Direct ΔΣ Receiver in 40 nm CMOS. *IEEE Journal of Solid-State Circuits*. 2015;50(3):644-655.

- [3] Ghaffari A., Klumperink E. A. M., Nauta B.. A differential 4-path highly linear widely tunable on-chip band-pass filter. *IEEE Radio Frequency Integrated Circuits Symposium*. 2010;:299-302.

- [4] Mirzaei A., Darabi H., Yazdi A., Zhou Z., Chang E., Suri P. A 65 nm CMOS Quad-Band SAW-Less Receiver SoC for GSM/GPRS/EDGE. IEEE Journal of Solid-State Circuits. 2011;46(4):950-964.

- [5] Borremans J., Mandal G., Giannini V., et al. A 40 nm CMOS 0.4-6 GHz Receiver Resilient to Out-of-Band Blockers. *IEEE Journal of Solid-State Circuits*. 2011;46(7):1659-1671.

- [6] Koli K., Jussila J., Sivonen P., Kallioinen S., Pärssinen A.: A 900MHz direct Delta-Sigma receiver in 65nm CMOS. IEEE International Solid-State Circuits Conference - (ISSCC). 2010;:64-65.

- [7] Nejdel A., Liu X., Palm M., et al. A 0.6-3.0GHz 65nm CMOS radio receiver with ΔΣ based A/D-converting channel-select filters. European Solid-State Circuits Conference (ESSCIRC), ESSCIRC 2015 - 41st. 2015;:299-302.

- [8] Chen R., Hashemi H.. Reconfigurable SDR receiver with enhanced front-end frequency selectivity suitable for intra-band and inter-band carrier aggregation. IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers. 2015;:1-3.

- [9] Wu C., Alon E., Nikolic B., A Wideband 400 MHz-to-4 GHz Direct RF-to-Digital Multimode Delta Sigma Receiver. *IEEE Journal of Solid-State Circuits*. 2014;49(7):1639-1652.

- [10] Ru Z., Moseley N. A., Klumperink E. A. M., Nauta B.. Digitally Enhanced Software-Defined Radio Receiver Robust to Out-of-Band Interference. *IEEE Journal of Solid-State Circuits*. 2009;44(12):3359-3375.

- [11] Haq F. U., Englund M., Stadius K., et al. A wideband blocker-resilient RF front-end with selective input-impedance matching for direct- ΔΣ-receiver architectures. *IEEE Nordic Circuits and Systems Conference (NORCAS)*. 2016;:1-4.

- [12] Zhu J., Krishnaswamy H., Kinget P. R.. Field-Programmable LNAs With Interferer-Reflecting Loop for Input Linearity Enhancement. IEEE Journal of Solid-State Circuits. 2015;50(2):556-572.

- [13] Park J. W., Razavi B., Channel Selection at RF Using Miller Bandpass Filters. IEEE Journal of Solid-State Circuits. 2014;49(12):3063-3078.

- [14] Park J. W., Razavi B., A 20mW GSM/WCDMA receiver with RF channel selection. *IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*. 2014;:356-357.

- [15] Park J., Kim S. N., Roh Y. S., Yoo C. A Direct-Conversion CMOS RF Receiver Reconfigurable From 2 to 6 GHz. IEEE Transactions on Microwave Theory and Techniques. 2010;58(9):2326-2333.

- [16] Rossi P., Liscidini A., Brandolini M., Svelto F. A variable gain RF front-end, based on a Voltage-Voltage feedback LNA, for multistandard applications. *IEEE Journal of Solid-State Circuits*. 2005;40(3):690-697.

- [17] Östman K.B., Englund M., Viitala O., Stadius K., Koli K., Ryynänen J.. Characteristics of LNA Operation in Direct Delta-Sigma Receivers. IEEE Transactions on Circuits and Systems II: Express Briefs. 2014;61(2):70-74.

- [18] Andrews C., Molnar A. C.. Implications of Passive Mixer Transparency for Impedance Matching and Noise Figure in Passive Mixer-First Receivers. IEEE Transactions on Circuits and Systems I: Regular Papers. 2010;57(12):3092-3103.

- [19] Forbes T., Ho W. G., Gharpurey R., Design and Analysis of Harmonic Rejection Mixers With Programmable LO Frequency. *IEEE Journal of Solid-State Circuits*. 2013;48(10):2363-2374.

- [20] Ostman K.B., Englund M., Viitala O., et al. Analysis and Design of N-Path Filter Offset Tuning in a 0.7åŧ2.7-GHz Receiver Front-End. IEEE Transactions on Circuits and Systems I: Regular Papers. 2015;62(1):234-243.

- [21] Nejdel A., Sjöland H., TörmÄdnen M. A Noise-Cancelling Receiver Front-End With Frequency Selective Input Matching. IEEE Journal of Solid-State Circuits. 2015;50(5):1137-1147.

[22] Andrews C., Molnar A.C., A Passive Mixer-First Receiver With Digitally Controlled and Widely Tunable RF Interface. *Solid-State Circuits, IEEE Journal* of. 2010;45(12):2696-2708.

**How cite this article:** Ul haq F, Östman K.B, Englund M, Stadius K, Kosunen M, Koli K, and Ryynänen J. A Common-Gate Common-Source Low Noise Amplifier Based RF Front-End With Selective Input-Impedance Matching for Blocker Resilient Receivers .

**TABLE 1** Front-end prformance summary

| Parameter                | This work <sup>7</sup> | Interferer reflecting loop LNA(13) | Miller bandpass filters LNA(12) |

|--------------------------|------------------------|------------------------------------|---------------------------------|

| Operating band (GHz)     | 0.7-2.7                | 0.2-1.6                            | 0.05-2.5                        |

| Conversion Gain (dB)     | 15                     | 13-22                              | 38                              |

| Power (mW)               | 11.5                   | 13                                 | 20                              |

| Supply voltage(V)        | 1                      | 1.6                                | 1.2                             |

| Baseband bandwidth (MHz) | 10                     | 20                                 | 0.35-20                         |

| Process                  | 28nm FDSOI             | 65nm CMOS                          | 65nm CMOS                       |

| Maximum NF (dB)          | 5.1                    | 3.6                                | 2.9                             |

| OB IIP3 (dBm)            | +141                   | +14.5 <sup>2</sup>                 | $+10^{3}$                       |

| BCP (dBm)                | -1.54                  | -4 <sup>5</sup>                    | 06                              |

1) First blocker at 100MHz offset from  $f_{LO}$  2) First blocker at 80MHz offset from  $f_{LO}$  3) First blocker at 20MHz offset from  $f_{LO}$  4) Blocker at 100MHz offset from  $f_{LO}$  5) Blocker at 80MHz offset from  $f_{LO}$  6) Blocker at 20MHz offset from  $f_{LO}$  7) Simulated response.  $\delta$