This is an electronic reprint of the original article. This reprint may differ from the original in pagination and typographic detail.

Kossifos, Kypros M.; Petrou, Loukas; Varnava, Giorgos; Pitilakis, Alexandros; Tsilipakos, Odysseas; Liu, Fu; Karousios, Petros; Tasolamprou, Anna C.; Seckel, Manuel; Manessis, Dionysios; Kantartzis, Nikolaos V.; Kwon, Do Hoon; Antoniades, Marco A.; Georgiou, Julius **Toward the Realization of a Programmable Metasurface Absorber Enabled by Custom Integrated Circuit Technology**

Published in: IEEE Access

DOI: 10.1109/ACCESS.2020.2994469

Published: 01/01/2020

Document Version Publisher's PDF, also known as Version of record

Published under the following license: CC BY

Please cite the original version:

Kossifos, K. M., Petrou, L., Varnava, G., Pitilakis, A., Tsilipakos, O., Liu, F., Karousios, P., Tasolamprou, A. C., Seckel, M., Manessis, D., Kantartzis, N. V., Kwon, D. H., Antoniades, M. A., & Georgiou, J. (2020). Toward the Realization of a Programmable Metasurface Absorber Enabled by Custom Integrated Circuit Technology. *IEEE Access*, *8*, 92986-92998. Article 9092996. https://doi.org/10.1109/ACCESS.2020.2994469

This material is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

Received March 27, 2020, accepted April 26, 2020, date of publication May 14, 2020, date of current version June 1, 2020. *Digital Object Identifier* 10.1109/ACCESS.2020.2994469

# **Toward the Realization of a Programmable Metasurface Absorber Enabled by Custom Integrated Circuit Technology**

KYPROS M. KOSSIFOS<sup>®</sup><sup>1</sup>, (Member, IEEE), LOUKAS PETROU<sup>®</sup><sup>1</sup>, GIORGOS VARNAVA<sup>®</sup><sup>1</sup>, ALEXANDROS PITILAKIS<sup>®</sup><sup>2,3</sup>, ODYSSEAS TSILIPAKOS<sup>®</sup><sup>2</sup>, (Senior Member, IEEE), FU LIU<sup>®</sup><sup>4</sup>, PETROS KAROUSIOS<sup>®</sup><sup>1</sup>, ANNA C. TASOLAMPROU<sup>®</sup><sup>2</sup>, MANUEL SECKEL<sup>®</sup><sup>5</sup>, DIONYSIOS MANESSIS<sup>®</sup><sup>5</sup>, NIKOLAOS V. KANTARTZIS<sup>®</sup><sup>2,3</sup>, (Senior Member, IEEE), DO-HOON KWON<sup>®</sup><sup>6</sup>, (Senior Member, IEEE), MARCO A. ANTONIADES<sup>®</sup><sup>1,7</sup>, (Senior Member, IEEE), AND JULIUS GEORGIOU<sup>®</sup><sup>1</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical and Computer Engineering, University of Cyprus (UCY), 1678 Nicosia, Cyprus

<sup>2</sup>Institute of Electronic Structure and Laser, Foundation for Research and Technology–Hellas (FORTH), 1110 Heraklion, Greece

<sup>3</sup>Department of Electrical and Computer Engineering, Aristotle University of Thessaloniki (AUTH), 54124 Thessaloniki, Greece

<sup>5</sup>Fraunhofer Institute for Reliability and Microintegration (IZM), 13355 Berlin, Germany

<sup>6</sup>Department of Electrical and Computer Engineering, University of Massachusetts at Amherst, Amherst, MA 01003, USA

<sup>7</sup>Department of Electrical, Computer and Biomedical Engineering, Ryerson University, Toronto, ON M5B 2K3, Canada

Corresponding author: Kypros M. Kossifos (kossifos.kypros@ucy.ac.cy)

This work was supported by the European Union's Horizon 2020 Future Emerging Technologies Call (FETOPEN-RIA) Project VISORSURF under Grant 736876.

**ABSTRACT** The realization of a programmable metasurface, enabled by a custom application-specific integrated circuit (ASIC), is presented in this paper. The ASIC is used to provide an adaptive complex impedance load to each of the metasurface unit cells. Various technology nodes are analyzed for the implementation of tunable complex impedance loading elements before one is selected for the final implementation, in which four complex loads are placed within each integrated circuit, and each load is controlled by two digital-toanalog converters. Furthermore, the ASICs populate the back of the metasurface to form a mesh network to enable programmability. The paper includes practical limitations that affect the realization, as well as an example adaptive metasurface absorber that builds upon the practical tuning range of the ASIC. Perfect absorption for both transverse electric and transverse magnetic polarization is demonstrated.

**INDEX TERMS** Metasurfaces, ASIC, programmable RF load, perfect absorption, reconfigurable.

#### **I. INTRODUCTION**

Metamaterials are composite materials that exhibit properties that are not found in nature. A negative refractive index is one of the many exotic properties that metamaterials possess. It was initially speculated in [1] and experimentally demonstrated in [2] that a negative refractive index can be realized when the electric permittivity and magnetic permeability are both negative. Metamaterials have also demonstrated the ability to resolve beyond the diffraction limit in free space [3] by designing the refractive index to be equal

The associate editor coordinating the review of this manuscript and approving it for publication was Yasar Amin<sup>(D)</sup>.

to -1, and cloaking by manipulating the electromagnetic waves around an object [4]. These are just some of highlights of the metamaterial properties. Metamaterials have since also been used to improve the performance of countless components in RF/microwave and antenna design ([5]–[8]).

Metasurfaces, the two-dimensional versions of metamaterials have gained interest by researchers in the past decade. Like their three-dimensional counterparts, they have demonstrated many exotic properties such as anomalous reflection [9]–[12], perfect absorption [13] and non-linear reflection [14]. By loading the metasurfaces with lumped elements the metasurface response can be altered [15]. These lumped elements can be replaced with tunable varactors

<sup>&</sup>lt;sup>4</sup>Department of Electronics and Computer Engineering, Aristone University of Thessatolink (AUTH), 94

or varistors and create electronically tunable metasurface reflectors [16], [17] and absorbers [18], [19]. Other means of obtaining tunable metasurfaces have been shown, like magnetic tunability [20], optical tunability [21] and even by exploiting the optomechanical properties of poly disperse red 1 acrylate to optically tune metasurfaces with a memory effect [22], [23].

Metasurfaces have demonstrated the ability to synthesize wavefronts through the individual design of their constituent unit cells. In [24] multi-beam reflection and simultaneous polarization conversion was demonstrated. Isoflux patterns with circular polarization were demonstrated in [25] and local multipoint distribution service patterns were demonstrated in [26].

Dynamic wavefront manipulation was also demonstrated by programmable metasurfaces. Dynamic scattering, focusing and polarization rotation was implemented in [27]. Dynamic control of the modulation of the reflection phase resulted in accurate control of the harmonic level of a non-linear reflecting metasurface [14]. Programmable metasurfaces were utilized to implement reflective [28] and transmissive [29] holograms in the microwave regime.

The conceptual design of this work was presented in [30], where individual electronically tunable complex impedance metasurface loading elements, consisting of resistive and capacitive (RC) elements, were embedded in each unit cell to obtain a reconfigurable multifunctional metasurface. It was shown that in using this approach, continuous control over the real and imaginary parts of the complex surface impedance can be obtained, thus enabling the shaping of the spatial profile of both the reflection amplitude and phase, leading to maximum versatility in the achievable functions. In this paper, the design methodology is presented, including the steps taken to implement the programmable metasurface concept by taking into account manufacturing and cost limitations. The programmable metasurface consists of a top textured layer, exposed to the EM waves, an intermediate ground plane layer, and two routing layers on the bottom, to provide control and power to the application-specific integrated circuits (ASIC) that are used to program the metasurface. The ASICs are populated on the bottom side in an array structure. In order to reduce the cost and to conform to tight space constraints, a single ASIC design must operate without the need for any further components. As will be subsequently elaborated upon, the ASIC contains both low-power, metasurface loading elements, as well as asynchronous circuits implementing a grid communication algorithm, as presented in [31]. This paper includes realistic loading element tunability ranges, extracted from three candidate semiconductor technology process design kits (PDKs). Furthermore, the paper outlines various metasurface PCB manufacturability issues. Finally the paper shows that the ASIC can be used to create a programmable metasurface, also known as a hypersurface [32], which demonstrates programmed perfect absorption, for a range of incident angles for both TE and TM polarizations.

# II. PROGRAMMABLE METASURFACE UNIT CELL

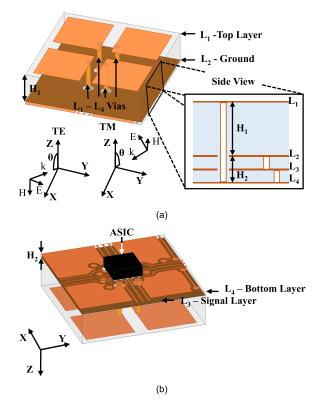

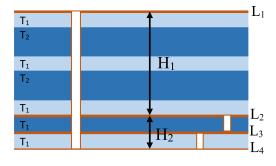

An example unit cell topology can be seen in Fig. 1. It consists of a textured metasurface pattern on the top layer  $(L_1)$ , a ground plane in the middle layer  $(L_2)$ , communication and power distribution layers  $(L_3 \text{ and } L_4)$ , with the ASIC bonded to the bottom layer  $(L_4)$ . The ASIC on the bottom layer, containing the metasurface loading elements, has four direct vias that route the RF signals between the bottom layer  $(L_4)$ and the top layer  $(L_1)$ .

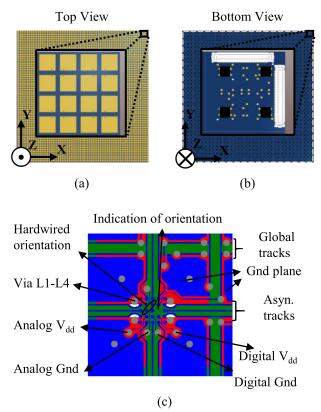

FIGURE 1. Metasurface unit cell geometry. (a) Top side of the unit cell and (b) bottom side of the unit cell showing the location of the metasurface loading application-specific integrated circuit (ASIC).

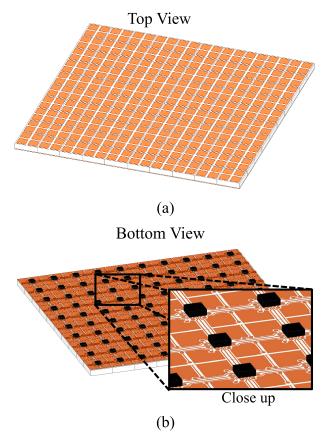

The example unit cell topology in Fig. 1, which has a subwavelength size of  $\lambda/7$ , is periodically repeated to form the complete metasurface that occupies a total area of  $5 \times 5 \lambda^2$ , at the design frequency (5 GHz). Fig. 2 shows an array of unit cells, with the top view, (a), showing the textured square patch pattern, while the bottom view, (b), shows the metasurface loading ASIC that is placed in every unit cell.

The general topology was chosen after carefully considering other available options, e.g. the ASIC could lie on the top layer or even be embedded within the PCB. The first example was discounted since having metallic tracks that carry power and communication signals on the top layer will adversely affect the electromagnetic behavior of the metasurface. Secondly, if the ASIC were to be embedded in the metasurface PCB, it would not only need a specialized, highcost, PCB process, but also would render the hypersurface irreparable in case of ASIC faults. Given the large number of

**FIGURE 2.** Illustration of a metasurface composed of  $10 \times 10$  unit cells. (a) Top side and (b) bottom side showing the metasurface loading ASICs.

ASICs needed to create a hypersurface, the probability of one ASIC failing or having a dry solder joint is increased. Thus, serviceability is of paramount importance in the selection of the topology.

The design cycle of a metasurface, like the one shown in Fig. 1, requires a careful design balancing act that takes into account multiple practical constraints. The metasurface presented is designed to perform as an absorber at normal and oblique incident angles. As it will be shown in section II.A, this entails that the loading ASIC will need to cover the required *RC* range for its operation. In the current example, the range required for the resistance is relatively low, and hence works at the limits of the practical range found in IC implementations, as it is shown in Section III. This constraint can be relaxed by implementing the hypersurface on a thicker substrate (H<sub>1</sub>) and by employing a substrate with lower dielectric losses, resulting in higher resistance value requirements. An example of the manufactured thicker PCB stack is shown in detail in Section IV.

#### A. DESIGN OF PROGRAMMABLE METASURFACE

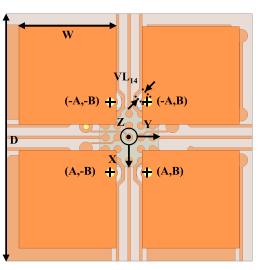

The example unit cell design is elaborated in Fig. 3. The details of the geometric parameters are listed in Table 1. An optimized parameter that is sensitive for the performance of the metasurface absorber is the position of the  $L_1$ - $L_4$  vias

FIGURE 3. Metasurface unit cell geometry. (a) Top side, (b) bottom side, and (c) close-up of the bottom side, showing the location of the metasurface loading ASIC.

(c)

connecting the patches in  $L_1$  to the ASIC terminals in  $L_4$ . As described in [33], the optimal position for an isotropic cell would be in the corner of the patches, where the surface current density is larger. Unfortunately, due to various fabri-

TABLE 1. Unit cell geometry.

| Geometric parameter | Dimensions (mm) | Description                                        |

|---------------------|-----------------|----------------------------------------------------|

| $H_1$               | 2.137           | Top Substrate Thickness                            |

| $H_2$               | 0.255           | Bottom Substrate Thickness                         |

| D                   | 8.4             | Period of the Unit Cell                            |

| W                   | 3.32            | Width of the Patch                                 |

| А                   | 1.2             | X-Coordinate of L1-L4 Via                          |

| В                   | 0.641           | Y-Coordinate of L <sub>1</sub> -L <sub>4</sub> Via |

| $VL_{14}$           | 0.30            | Diameter of L <sub>1</sub> -L <sub>4</sub> Via     |

| $VL_{24}$           | 0.15            | Diameter of L <sub>2</sub> -L <sub>4</sub> Via     |

| IC <sub>D</sub>     | 2.00            | IC Dimensions                                      |

| IC <sub>P</sub>     | 0.40            | IC Pitch                                           |

| IC <sub>B</sub>     | 0.25            | IC Pad Diameter                                    |

cation limitations this option was not available, so the vias were placed near the inner edge of patches along one direction, as shown in Fig. 3, so that at least one polarization would be optimally covered. The methodology for the optimization of the "free" absorber unit-cell parameters, namely the width of the patches and the period of the cell, is described in [33], under the constraints of: operating frequency, manufacturing (through via position), dielectric thicknesses, IC size and available RC range.

In Fig. 3(a) and (b) a top and bottom view of the unit cell and is shown. Fig. 3(c) depicts the connectivity of the ASIC to the metasurface from the edge pins. The ASIC in this design loads the metasurface with four parallel-connected RC loads, as shown in Fig. 3(c). The design of the metasurface loads, along with their control circuit will be discussed in Section III.

The IC uses wafer level chip scale packaging (WLCSP). The solder balls are also included in the simulations, and are each modelled as a cylinder of height 0.15 mm and diameter 0.25 mm. The solder ball used was alloy SAC405 in order to accurately take into account its effect on the design.

The realizable unit cell was designed by taking into account practical limitations of the ASIC and the PCB technology. These limitations include R and C ranges, cost of the semiconductor process, maximum PCB thickness, via and track sizes, and substrate losses.

As can be seen in Table 1,  $H_1$  is much larger than  $H_2$ , in order to relax the ASIC's constraint on the realization of the resistance values, and  $H_2$  should be small, so that the power and ground supplied to the ASIC is of good quality. The asymmetric layer stack of the PCB improves the RF performance of the metasurface, however care must be taken with an increased number of layers as they introduce additional variations in the PCB thickness.

The metasurface unit cell was co-simulated using an electromagnetic model that was combined with the lumped *RC* loads. The absorbance performance, shown in Fig. 4, was obtained through the use of circuit and electromagnetic co-simulations in CST. The unit cell simulations take into account the existence of traces and metallic fill layers that are implemented in Altium Designer and checked to comply with

**FIGURE 4.** Reflection coefficient magnitude in dB at 5 GHz for (a) normal incidence, (b) TE  $\theta$  = 30°, (c) TE  $\theta$  = 45°, (d) TE  $\theta$  = 65°, (e) TM  $\theta$  = 30° and (f) TM  $\theta$  = 45°.

the PCB design rules. These traces are used for signaling, power and communication. More information on the use of these traces can be found in Section IV.

The example unit cell geometry targeted a perfect absorber at a design frequency of 5 GHz. At this frequency, absorption of TE-polarized waves (see legend in Fig. 1) was studied at various angles of  $\theta$  while keeping the angle  $\varphi = 0^{\circ}$ , corresponding to the *xz*-incidence plane with reference to Fig. 3(a). The absorption of TM-polarized waves was studied at various angles of  $\theta$  at an orthogonal plane with respect to the TE polarization ( $\varphi = 90^{\circ}$ ), corresponding to the yz-incidence plane with reference to Fig. 3(a). This discrimination between the TE and TM planes of incidence is caused by the asymmetric connection (in the x- and y-directions) of the L1-L4 vias to the metasurface patches on the top layer, as shown in Fig. 3(a). The discrimination between the TE and TM planes for y-polarized incidence arose as a tradeoff between fabrication limitations, available loading impedance ranges and our target for angle-tunable perfect absorption for at least one polarization [33]. Oblique TM polarization has narrower angle tunability due to the E-field component parallel to the vertical vias (L1-L4 and L4-L2) which gives rise to currents and mutual coupling between the lateral traces of the grounding and RF terminals (in L4). Finally, x-polarized incidence in both TE and TM planes will severely

underperform due to the trade-off mentioned; the physical reason is the large distance of the through vias to the edges of the patches along the x-axis, Fig. 3(a).

In Fig. 4(a) the reflection coefficient for normal incidence ( $\theta = 0^{\circ}$ ) is shown, indicating that perfect absorption  $(|\mathbf{r}| < -30 \text{ dB})$  is obtained at the center of the plotted RC range. Note that the result is almost indistinguishable for TM polarization, but not identical due to the asymmetric placement (in the x- and y-axes) of the  $L_1$ - $L_4$  vias with respect to the metasurface patches on the top layer (Fig. 3(a)), something that was done to obtain good performance for large oblique incidence angles for at least one, the TE, polarization, see also [33]. This can be seen in Fig. 4(b), (c) and (d) where the reflection coefficient for TE polarization is shown for  $\theta = 30^{\circ}, 45^{\circ}$  and  $60^{\circ}$ , respectively. It can be seen that the required resistance and capacitance for perfect absorption increase for larger oblique angles of incidence, but a very low reflection amplitude can be obtained inside the considered RC range. Note that two absorption peaks appear for larger angles and can be both exploited [33]. In Fig. 4(e) and (f) the reflection coefficient for TM polarization is shown for  $\theta = 30^{\circ}$  and  $45^{\circ}$ , respectively. It can be seen that the required RC combination shifts towards higher capacitances for larger oblique angles of incidence. For this polarization, the reflection dip moves outside the considered RC range for angles exceeding 45° degrees, which could prove to be a limitation in the realization of the loading-element values.

#### **III. METASURFACE LOADING ASIC**

Numerous semiconductor technologies are commercially available for the implementation of the metasurface loading ASICs. The selection of a semiconductor technology offers new challenges in the design of a suitable integrated circuit for metasurface applications. Programmable metasurface designs, shown in the literature thus far, use commercial-offthe-shelf (COTS) components as loading elements, and programmable modules such as field-programmable gate arrays (FPGAs), to individually address each unit cell [14], [27]. This type of architecture separates the high-frequency RF electronic component of the design (the unit cell loading element) from the low-frequency analog and digital component (the FPGA). Typically, the RF loading elements operate at a higher frequency and are manufactured from high-performance and costly technologies, like silicongermanium (SiGe) and even gallium-arsenide (GaAs), while the analog and digital control circuits are manufactured on cheaper silicon technologies.

This paper aims towards the realization of a programmable metasurface architecture that addresses individually each unit cell, and is capable of providing a complex loading impedance. This functionality necessitates that the high frequency loading elements are integrated together with the analog and digital control circuits on the same chip. Ideally, in order to realize high-quality RF loading elements, the whole integrated circuit would be designed in a highfrequency SiGe or GaAs process, however the large number of integrated circuits necessary to implement a large hypersurface would render the cost prohibitively high; therefore, a technology should be selected that can provide a sufficient range for the tunable complex impedance loading elements at the design frequency of 5 GHz, while also being economically feasible.

With the envisaged large number of ASICs needed for the hypersurface implementation, the power consumption of each IC needs to be carefully considered. In [27], each individual metasurface loading element required 10 mA of current in its ON state. This might appear small, but the metasurface consists of  $40 \times 40$  unit cells, which translates to a total current consumption of 16 A, when all 1600 loading elements are ON. In order to reduce the overall current consumption, each metasurface loading element should be implemented with a negligible current draw, and since each unit cell is locally controlled, the digital and analog part should also be designed with minimum power requirements. In [34], the importance of using asynchronous control circuits for enabling programmable and scalable metasurfaces is argued. Asynchronous circuits offer a low power consumption for controllers that are idling most of the time, as in the case of controllable metasurfaces. Additionally, and more importantly for RF applications, electromagnetic emissions from this ASIC are inherently reduced, due to the data-driven clocking, as well the fact that a location setting can be changed without clocking the entire surface. Finally, by using asynchronous clocking there is no need for a power hungry clock distribution network on the entire metasurface.

The packaging of the metasurface loading ASIC also needs to be taken in to account. The package will introduce additional parasitic affects that will reduce the overall range of the obtainable complex impedances, and can also increase the cost of the IC. For the chosen metasurface application, wafer level chip scale packaging (WLCSP) was chosen since it offers the cheapest packaging solution and introduces the least amount of parasitic affects [35], [36].

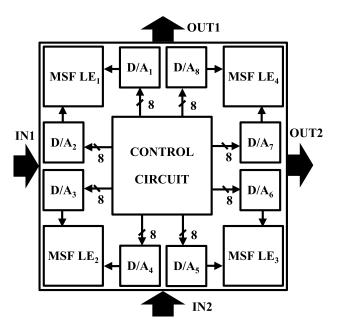

The top-level block diagram of the metasurface loading ASIC is shown in Fig. 5. It consists of four metasurface loading elements that consist of a voltage-controlled capacitor (varactor) in parallel with a voltage-controlled resistor (varistor). These LEs are connected between the outer pins of the chip and the center ground pin. The biasing for the metasurface loading elements is provided by eight on-chip digital-to-analog converters, that are set by data passed through four serial, asynchronous, unidirectional communication ports of the ASIC. These communication ports form a larger grid, within the metasurface, arranged in a Manhattan style architecture, as described in Section III B.

# A. DESIGN OF METASURFACE LOADING ELEMENTS

In this section, an investigation is presented for three commercially-available candidate technologies. This is done using simulated results from Cadence Virtuoso, revealing the achievable complex impedance ranges for the metasurface loading elements. These are CMOS processes at the 350 nm,

FIGURE 5. Top-level diagram of the metasurface loading ASIC showing the input/output (IN1, IN2, OUT1, OUT2), the four metasurface loading elements (MSF LEs), eight digital-to-analog converters (D/As), and the communication control circuit. The ASIC uses serial and unidirectional input/output communication.

180 nm and 65 nm technology nodes. Specialized SiGe and GaAs technologies are not investigated in this work, since they are costly and not widely available.

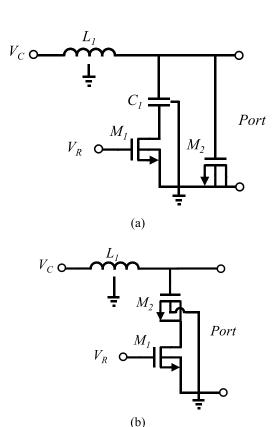

The metasurface loading element uses a MOSFET varactor to adjust the imaginary part of the complex impedance and a MOSFET varistor to control the real part of the complex impedance. These tunable elements can be placed either in a parallel topology (Fig. 6(a)) or a series topology (Fig. 6(b)). In both topologies the MOSFET varistor  $(M_1)$  is adjusted through a voltage supplied to its gate, V<sub>R</sub>. The MOSFET varactor  $(M_2)$  is supplied by voltage V<sub>C</sub> through an RF choke inductor  $(L_1)$ . The parallel configuration uses an additional DC block capacitor ( $C_1$ ) to prevent the biasing voltage  $V_C$ from shorting through the varistor  $(M_1)$  when  $V_R$  is applied to its gate. In both of these topologies the steady-state current draw is mainly attributed to gate leakage and is negligible.

The supplied voltages V<sub>R</sub> and V<sub>C</sub> are progressively increased from zero to the maximum allowed operating voltage of the technology or to a large enough voltage that does not provide any further impedance tuning. For each set of  $V_R$  and  $V_C$  voltages, this corresponds to a specific RCcombination. Thus, by varying both V<sub>R</sub> and V<sub>C</sub>, an area of RC combinations can be created within an RC map, which defines the achievable RC values for that technology.

The RC area of each loading element needs to cover the optimum RC combinations required by the metasurface unit cell to achieve perfect absorption, which are shown in Fig. 4. This has proven difficult to achieve in simulations with the series configuration (in all three of the evaluated technologies), since the varistor  $(M_1)$  needs to have a large number of fingers to achieve the required low resistance.

FIGURE 6. Two simplified metasurface loading element circuit topologies, (a) parallel topology and (b) series topology. Both consist of an RF choke (L1), varistor (M1) and varactor (M2). The circuit of (a) includes an additional DC block capacitor (C1).

The large number of fingers also means that its parasitic capacitance to the substrate is also moderately large, thus effectively short-circuiting it at the design frequency.

The parallel configuration showed more promise in achieving the required low resistance. In order to evaluate the performance of each technology, each device  $(M_1, M_2, L_1, C_1)$ was adjusted to increase the parallel RC range and satisfy the optimum RC combinations.

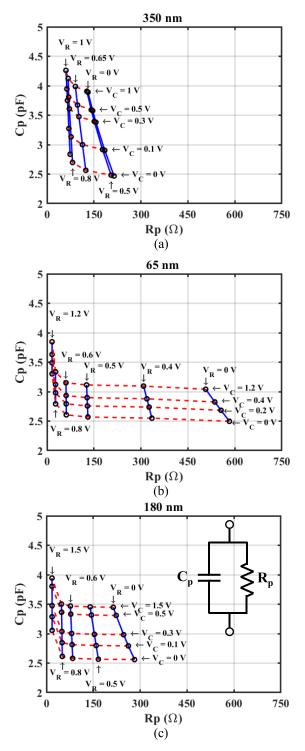

The adjusted parallel configuration RC ranges can be seen in Fig. 7 (a), (b) and (c) for the 350 nm, 65 nm and 180 nm technologies, respectively. The results of Fig. 7 were obtained using data from S-parameter simulations and converting the reflection coefficient at the Port on the right-hand side of the parallel loading element circuit of Fig. 6(a) to a parallel configuration RC map. With this conversion to a simple equivalent parallel configuration, consisting of a simple parallel RC circuit, all the complex technology device models collapse into a single RC map that can be easily compared between the different technologies, and can be used to evaluate the metasurface performance. Constant V<sub>R</sub> lines are shown in solid blue lines in the Fig. 7, and constant V<sub>C</sub> lines are shown in dashed red lines.

It can be seen in Fig. 7 that for larger feature technologies the capacitance range increases, while the resistance range decreases. The reduction of the resistance range in the larger feature technologies is caused by a reduction of the quality

FIGURE 7. Equivalent parallel resistance and capacitance range for (a) 350 nm, (b) 65 nm and (c) 180 nm technologies.

factor of  $M_2$  due to the larger gate length [37]. The gate width also increases the capacitance range proportionally [37]. It is obvious that there is a compromise to be made when choosing the technology. The 180 nm technology offers a compromise between the achievable capacitance and resistance ranges, and was therefore chosen as a viable technology. With the achieved RC range show in Fig. 7(c), the metasurface can absorb transverse electric and transverse magnetic polarizations at the planes of incidence shown in Fig. 1 up to oblique angles of  $45^{\circ}$  for the TE polarization and up to  $25^{\circ}$ for the TM polarization.

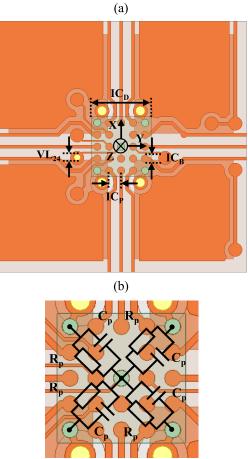

As described in Section II A there are four metasurface LEs in each ASIC, connected as shown in Fig. 3(c) or Fig. 8(a). The ASIC uses 19 pins for the controller and the remaining 5 for the LEs. An alternative solution considered, had two metasurface loading elements as shown in Fig. 8(b), however we chose that shown in (a) in order to increase the equivalent parallel resistance of the circuit. The parallel resistance of Fig. 8(a) is essentially double that of Fig. 8(b). Additionally, two of the pins of Fig. 8(b) would have to be converted to a DC ground, using two additional inductors (RF chokes). Note that on-chip inductors occupy an area comparable to the WLCSP pads, which will make the LEs occupy a larger area on-chip. This increased LE area will increase the ASIC's size as well as its cost. Furthermore, the layout implementation of Fig. 8(b) will suffer from additional parasitics, arising from metal lines running across the entire IC. In order to maintain the rotational symmetry required, to allow the chip to be rotated for communication purposes (see Fig. 9), the center pin was selected as the RF ground. A further alternative considered is shown in Fig. 8(c). Although this option needs one fewer pin, it was also abandoned because it would be impossible to independently control the varactors/varistors

**FIGURE 8.** (a) Selected metasurface loading element pin location and configuration. (b) and (c) are alternative pin location options.

**FIGURE 9.** A 4  $\times$  4 grid with two gateways and wraparounds forming a network. Letters *a*, *b*, *c* and *d* correspond to the orientation of each node.

without additional space-hungry on-chip inductors and DC block capacitors.

# B. INTEGRATED METASURFACE LOADING ELEMENT CONTROL CIRCUIT AND DIGITAL-TO-ANALOG CONVERTERS

The integrated metasurface loading element control circuit is presented in this section along with the digital-to-analog converters. The control circuit operation involves the routing of data packages in a grid network where the payload of the package is the eight, single-byte inputs for the eight digital-to-analog converters, which in turn connect to the four analog  $V_R$  and four  $V_C$  voltages of the four loading elements.

Therefore, the control circuit has two main operations. First to provide the digital input to the digital-to-analog converter and in turn to tune the complex impedance of the unit cell. Second is to send or receive data packets to / from neighboring nodes in order to deliver the payload to the appropriate node of the network.

The ASIC control circuitry takes into account constraints arising both in the application and the manufacturability of the ASIC. Also, asynchronous communication is necessary because using a crystal oscillator and clock signal for synchronization (synchronous communication), can contribute to high power consumption, high EM noise generation and prevent the scalability of the metasurface. Given the large number of dies required to populate the metasurface, a relatively low-cost technology is needed and the die size needs to be as small as possible, to maximize the number of IC's per wafer. Also, the size must be large enough to be handled by automated pick-and-place machinery. A 2 mm  $\times$  2 mm size was selected, and so the maximum available WLCSP solder bumps that can be accommodated in this area is 25. To accommodate these restrictions, the control circuit has two serial input channels and two serial output channels, as shown in Fig. 5. Also, the current implementation is fully asynchronous, and the communication is carried out by handshaking between the transmitter node and the receiver node.

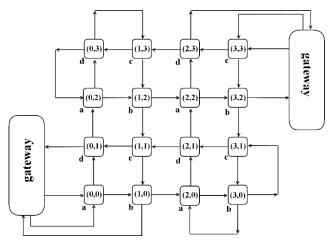

Each control circuit is part of a grid that intelligently moves packets to the destination node and configures the complex impedance values that are used as inputs to the varistors and varactors. In Fig. 9 a  $4 \times 4$  grid network of metasurface loading ICs is shown. The nodes have four orientations (a, b, c and d). This way, the network can be formed by designing only one control circuit. The corner nodes are connected using wraparounds to ensure that there is more than just one path to reach every node in the grid. Therefore, even when a node is faulty, the network will not collapse. The gateways are the means to convey packets to the grid and they have full computing capabilities and resources. They are responsible for feeding the packets into the network, receiving the packets, applying fault detection mechanisms or even acting as an intermediate node in the network. The network can adopt intelligent routing algorithms, so that the configuration of all unit cells is done fast and reliably. In [31], the authors present two routing algorithms with fault tolerance mechanisms that can be adopted by the control circuits used in this design.

The data packet, once received by the destination node, is temporarily stored in the node's buffer until verification confirms that the entire packet has been received with no errors. Then, the configuration bits are copied to the memory.

The stored bits directly drive the 8-bit digital-to-analog converter, producing the analog voltages needed to configure the LEs. A two-stage resistor string digital-to-analog converter architecture was adopted for the eight digital-toanalog converters. The digital-to-analog converter's output needs to be monotonic, accurate and it needs to occupy a small area in the IC. The current required by the metasurface loading element is negligible, therefore the digital to analog converter has no need of an output buffer. This requirement and its simplistic design made the two-stage resistor string digital-to-analog converter an attractive solution.

The analog voltages produced by the digital-to-analogue converters are inputs to the metasurface loading elements ( $V_R$  and  $V_C$  biases). This changes the metasurface loading element impedance, which in turn alters the metasurface surface impedance.

#### **IV. MANUFACTURABILITY OF METASURFACE PCB**

This section describes the production processes toward manufacturing the actual metasurface in a large industrial printed circuit board (PCB) format. The metasurface periodic sub-wavelength structure and its anisotropic PCB stack up are demanding, and push the capabilities of the manufacturing process. Asymmetric PCB layer stacks are commonly avoided since the different thermal expansion coefficients of the PCB materials and or the metallization will produce a warped PCB. The asymmetric PCB layer stack pushed for homogenous material layers shown in Fig 10. The PCB stack consists of Megtron 7N materials (Fig. 10), R-5785(N) laminate and prepreg R-5680(N) with thicknesses of  $T_1$ :100 $\mu$ m and  $T_2$ :750 $\mu$ m. The laminate R-5785(N) and the prepreg R5680(N) have the same electrical properties, dialectic constant of 3.35 ( $\varepsilon_r$ ) and a dissipation factor of 0.002 (tan( $\delta$ )). This makes the layering across the thickness H<sub>1</sub> and H<sub>2</sub> act as an electrically homogenous material.

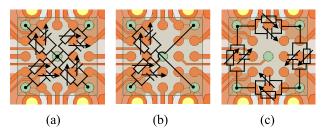

The four-layer PCB presented, consists of four metal layers as shown in Fig. 1. In terms of electrical connectivity,  $L_3$  and  $L_4$  serve for routing, while also a plane is positioned on  $L_3$  that is connected to  $V_{dd}$  and on  $L_4$  a metal fill is placed that is connected to the ground ( $L_2$ ).  $L_4$  includes the chips' footprints with the routing of the tracks for the asynchronous communications and global signals. The remaining area of  $L_4$  is covered with copper fillers that are connected to the ground. In addition, the three global tracks are distributed to the whole tile. The dimensions of the PCB are 302.4 × 302.4 mm, which translate to approximately  $5 \times 5 \lambda^2$ , at the design frequency (5 GHz). A top and bottom view of the PCB can be seen in Fig. 11 (a) and (b), respectively.

In Fig. 11 (c) the routing of the chips' pads is shown. An array of  $5 \times 5$  pads is used as the footprint of the WLCSP

Laminate: R-5785 (N) Prepreg: R-5680 (N)

FIGURE 10. The 4-layer PCB stack adopted for the example metasurface design.

**FIGURE 11.** Metasurface PCB, (a) top view, (b) bottom view, and (c) routing of chip's pads.

dies. The diameter of the pads is 0.25 mm with a pitch of 0.4 mm (center to center). One of the pads is not used to indicate the correct orientation of the chip. The track width within the chip's footprint is 0.045 mm to enable proper distribution of the tracks. The four corner pads are connected to  $L_1$  through  $L_1$ - $L_4$  vias. Three pads on each side are used for the asynchronous communication with the neighboring chips. Another two pads are dedicated to the global signals. Additional two pads are used for digital  $V_{dd}$  and Gnd and two pads for the analog  $V_{dd}$  and Gnd. The orientation of each chip is hardwired by two pads to  $V_{dd}$  or Gnd. When populating the board, the chips actual orientation can be

distinguished by the asymmetry of the pads, where one ball of the 25 is intentionally omitted. Asynchronous tracks are symmetrically routed to match the delays between lines.

Four unit cells are arranged in a scalable design with the appropriate orientation of the chips  $\begin{pmatrix} D & C \\ A & B \end{pmatrix}$ . Starting from the A position, the chips are rotated 90 degrees clockwise from A to D position. At the edges of the PCB, multiple Low Insertion Force (LIF) connectors are placed to enable the connection to neighboring PCBs. Thus, scalability can be achieved. These connectors can also be used for the connection of the gateway. In addition, pads dedicated to power tracks are distributed all over the edges of the PCB for better distribution of the power.

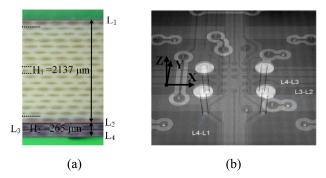

Even though the metallization layers are not symmetric in the PCB stack, the PCB showed very little warpage, and the warpage was less than  $100\mu$ m. A post fabrication crosssection of the PCB is shown in Fig. 12. The PCB stack thickness deviated from the nominal PCB thickness. This is mainly attributed to a deviation in the prepreg and lamination thicknesses in the stack compared to the nominal thicknesses, and to slightly larger copper thicknesses after electroplating on the copper layers. The measured H<sub>1</sub> and H<sub>2</sub> thicknesses used in the electromagnetic simulations can be seen in Fig. 12 (a).

**FIGURE 12.** (a) Cross-section of the 4-layer stack, and (b) X-ray of the manufactured PCB.

In Fig. 12 (b) an X-ray picture of the Hypersurface PCB was taken to validate that the  $L_1$ - $L_4$ ,  $L_2$ - $L_3$  and  $L_3$ - $L_4$  vias were successfully electroplated.

## V. METASURFACE PERFORMANCE

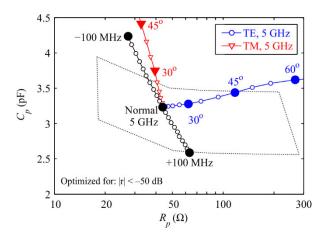

The functional metasurface performance can be seen in Fig. 13, where the optimal RC values for absorption are overlaid with the 180-nm semiconductor process range to demonstrate the capabilities of this example unit cell. The optimum RC combination for minimizing reflection (maximum absorption) is plotted with blue circular (TE) and red triangular markers. As can be seen, the unit cell can absorb perfectly at the target frequency of 5 GHz both normal and oblique incident waves of TE and TM polarization for angles up to 45 and 25 degrees, respectively [Fig. 13(a)]. The TE angle range is larger, given that this was the target polarization in the design process.

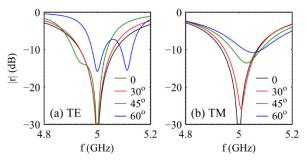

The performance is further examined in Fig. 14, where the reflection coefficient is plotted for various angles of incidence

FIGURE 13. Required loading-element RC values for perfect absorption of y-polarized oblique incidence for both TE and TM polarizations at 5 GHz.

FIGURE 14. Reflection spectra for optimal RC values within the range provided by the ASIC, for oblique incidence at the (a) TE and (b) TM polarizations.

as a function of frequency, considering the optimum RC load for each case. At normal incidence the reflection coefficient is less than -50dB. This degrades as the angle of incidence increases, as shown in Fig. 14(a) for TE polarization. However, it remains below -30 dB for incident angles up to 45 degrees, that can be covered with the 180 nm technology, accommodating the majority of RCS reduction applications. Similar behavior is found for the TM polarization, depicted in Fig. 14(b). The reflection coefficient at 5 GHz remains below -20 dB up to 25 degrees, that can be covered with the 180 nm technology.

Finally, the optimal RC values for normal incidence are plotted in Fig. 13 for  $\pm 100$ MHz to illustrate the frequency effect on the RC values. The bandwidth that can be accommodated for normal incidence is approximately 150 MHz around the target frequency of 5 GHz.

For this given metasurface example design, the targeted polarization affects the technology selection. From Fig. 12, it can be seen that TM polarization does not need large resistance tunability, but requires a larger capacitance range. If emphasis were to be placed on the TM polarization, then the 350 nm technology would have been more appropriate. The 350 nm technology can easily be adapted to a TM polarization absorber, and is more affordable. Similarly, for solely TE polarization performance, the 65 nm technology is more appropriate, since TE requires a larger resistance tuning range

**VOLUME 8, 2020**

and a lower capacitance range. As the semiconductor manufacturing costs increase exponentially with decreasing feature sizes, a tradeoff results in the choice of the 180 nm technology. This can satisfy large angles of incidence that would be suitable for the majority of RCS reduction applications.

# **VI. CONCLUSION**

An example programmable metasurface absorber design has been presented and has been used to demonstrate the feasibility of a low-cost, low-power ASIC design for adaptive metasurfaces. The ASIC design has been explored for various technology nodes at 350 nm, 180 nm, and 65 nm, where the performance has been evaluated in view of implementing realizable tunable complex impedance loading elements. After selecting the appropriate 180 nm semiconductor process technology, it has been demonstrated that perfect absorption can be achieved (-50 dB reflection coefficient)at normal incidence as well as at oblique angles up to  $45^{\circ}$  for TE polarization.

## **VII. CONTRIBUTIONS**

The multidisciplinary work presented in this work had contributors from eight institutions requiring much interaction. Authors affiliated with UCY predominantly contributed to the ASIC design, actual PCB layouts for production, and chip powering/communication/networking aspects. Authors affiliated with FORTH and Aalto predominantly contributed to the metasurface electromagnetic design, related PCB material specifications, the unit cell geometry and absorber performance evaluation. Authors affiliated with IZM provided fabrication guidelines for the design, and handled the PCB manufacturing.

#### ACKNOWLEDGMENT

The authors like to thank the partners in the VISORSURF consortium, Prof. S. Tretyakov, M. S. Mirmoosa, C. Liaskos, Prof. M. Kafesaki, and Prof A. Pitsilides for useful discussions.

#### REFERENCES

- [1] V. G. Veselago, "The electrodynamics of substances with simultaneously negative values of  $\epsilon$  and  $\mu$ ," Sov. Phys. Uspekhi, vol. 10, no. 4, pp. 509-514, Apr. 1968.

- [2] R. A. Shelby, D. R. Smith, and S. Schultz, "Experimental verification of a negative index of refraction," Science, vol. 292, no. 5514, pp. 77-79, Apr. 2001.

- [3] A. K. Iyer and G. V. Eleftheriades, "Free-space imaging beyond the diffraction limit using a Veselago-Pendry transmission-line metamaterial superlens," IEEE Trans. Antennas Propag., vol. 57, no. 6, pp. 1720-1727, Jun. 2009.

- [4] D. Schurig, J. J. Mock, B. J. Justice, S. A. Cummer, J. B. Pendry, A. F. Starr, and D. R. Smith, "Metamaterial electromagnetic cloak at microwave frequencies," Science, vol. 314, no. 5801, pp. 977-980, Nov. 2006

- [5] M. A. Antoniades and G. V. Eleftheriades, "Compact linear lead/lag metamaterial phase shifters for broadband applications," IEEE Antennas Wireless Propag. Lett., vol. 2, pp. 103-106, 2003.

- A. Grbic and G. V. Eleftheriades, "A backward-wave antenna based on [6] negative refractive index L-C networks," in Proc. IEEE Antennas Propag. Soc. Int. Symp., vol. 4, Jun. 2002, pp. 340-343.

- [7] K. M. Kossifos and M. A. Antoniades, "A NRI-TL metamaterial leaky-wave antenna radiating at broadside with zero beam-squinting," *IEEE Antennas Wireless Propag. Lett.*, vol. 17, no. 12, pp. 2223–2227, Dec. 2018.

- [8] F. Qureshi, M. A. Antoniades, and G. V. Eleftheriades, "A compact and low-profile metamaterial ring antenna with vertical polarization," *IEEE Antennas Wireless Propag. Lett.*, vol. 4, no. 1, pp. 333–336, 2005.

- [9] A. M. H. Wong and G. V. Eleftheriades, "Perfect anomalous reflection with a bipartite Huygens' metasurface," *Phys. Rev. X*, vol. 8, no. 1, Feb. 2018, Art. no. 011036.

- [10] S. Sun, K.-Y. Yang, C.-M. Wang, T.-K. Juan, W. T. Chen, C. Y. Liao, Q. He, S. Xiao, W.-T. Kung, G.-Y. Guo, L. Zhou, and D. P. Tsai, "High-efficiency broadband anomalous reflection by gradient meta-surfaces," *Nano Lett.*, vol. 12, no. 12, pp. 6223–6229, Dec. 2012.

- [11] O. Tsilipakos, A. C. Tasolamprou, T. Koschny, M. Kafesaki, E. N. Economou, and C. M. Soukoulis, "Pairing toroidal and magnetic dipole resonances in elliptic dielectric rod metasurfaces for reconfigurable wavefront manipulation in reflection," *Adv. Opt. Mater.*, vol. 6, no. 22, Nov. 2018, Art. no. 1800633.

- [12] A. Díaz-Rubio, V. S. Asadchy, A. Elsakka, and S. A. Tretyakov, "From the generalized reflection law to the realization of perfect anomalous reflectors," *Sci. Adv.*, vol. 3, no. 8, Aug. 2017, Art. no. e1602714.

- [13] D. Zhirihin, C. Simovski, P. Belov, and S. Glybovski, "Mushroom highimpedance metasurfaces for perfect absorption at two angles of incidence," *IEEE Antennas Wireless Propag. Lett.*, vol. 16, pp. 2626–2629, 2017.

- [14] J. Zhao, X. Yang, J. Y. Dai, Q. Cheng, X. Li, N. H. Qi, J. C. Ke, G. D. Bai, S. Liu, S. Jin, A. Alù, and T. J. Cui, "Programmable time-domain digitalcoding metasurface for non-linear harmonic manipulation and new wireless communication systems," *Nat. Sci. Rev.*, vol. 6, no. 2, pp. 231–238, Mar. 2019.

- [15] X. Chen, Y. Li, Y. Fu, and N. Yuan, "Design and analysis of lumped resistor loaded metamaterial absorber with transmission band," *Opt. Express*, vol. 20, no. 27, p. 28347, Dec. 2012.

- [16] C. Mias and J. H. Yap, "A varactor-tunable high impedance surface with a resistive-lumped-element biasing grid," *IEEE Trans. Antennas Propag.*, vol. 55, no. 7, pp. 1955–1962, Jul. 2007.

- [17] D. F. Sievenpiper, J. H. Schaffner, H. J. Song, R. Y. Loo, and G. Tangonan, "Two-dimensional beam steering using an electrically tunable impedance surface," *IEEE Trans. Antennas Propag.*, vol. 51, no. 10, pp. 2713–2722, Oct. 2003.

- [18] Z. Luo, L. Zhao, C. Xue, and D. Sievenpiper, "An electrically tunable absorbing metasurface for surface waves and plane waves," in *Proc. Asia– Pacific Microw. Conf. (APMC)*, Dec. 2016, pp. 1–4.

- [19] I. V. Shadrivov, P. V. Kapitanova, S. I. Maslovski, and Y. S. Kivshar, "Metamaterials controlled with light," *Phys. Rev. Lett.*, vol. 109, no. 8, Aug. 2012, Art. no. 083902.

- [20] H. Yang, T. Yu, Q. Wang, and M. Lei, "Wave manipulation with magnetically tunable metasurfaces," *Sci. Rep.*, vol. 7, no. 1, pp. 1–6, Dec. 2017.

- [21] F. Hu, W. J. Otter, and S. Lucyszyn, "Optically tunable THz frequency metamaterial absorber," in *Proc. 40th Int. Conf. Infr., Millim., THz Waves* (*IRMMW-THz*), Aug. 2015, pp. 1–2.

- [22] K. M. Kossifos, M. A. Antoniades, J. Georgiou, A. H. Jaafar, and N. T. Kemp, "An optically-programmable absorbing metasurface," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2018, pp. 1–5.

- [23] J. Georgiou, K. M. Kossifos, M. A. Antoniades, A. H. Jaafar, and N. T. Kemp, "Chua mem-components for adaptive RF metamaterials," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2018, pp. 1–5.

- [24] H. F. Ma, Y. Q. Liu, K. Luan, and T. J. Cui, "Multi-beam reflections with flexible control of polarizations by using anisotropic metasurfaces," *Sci. Rep.*, vol. 6, no. 1, p. 39390, Dec. 2016.

- [25] G. Minatti, S. Maci, P. De Vita, A. Freni, and M. Sabbadini, "A circularlypolarized isoflux antenna based on anisotropic metasurface," *IEEE Trans. Antennas Propag.*, vol. 60, no. 11, pp. 4998–5009, Nov. 2012.

- [26] D. R. Prado, M. Arrebola, M. R. Pino, and F. Las-Heras, "Improved reflectarray phase-only synthesis using the generalized intersection approach with dielectric frame and first principle of equivalence," *Int. J. Antennas Propag.*, vol. 2017, pp. 1–11, 2017.

- [28] L. Li, T. Jun Cui, W. Ji, S. Liu, J. Ding, X. Wan, Y. B. Li, M. Jiang, C.-W. Qiu, and S. Zhang, "Electromagnetic reprogrammable codingmetasurface holograms," *Nature Commun.*, vol. 8, no. 1, p. 197, Dec. 2017.

- [29] K. Chen, Y. Feng, F. Monticone, J. Zhao, B. Zhu, T. Jiang, L. Zhang, Y. Kim, X. Ding, S. Zhang, A. Alù, and C.-W. Qiu, "A reconfigurable active Huygens' metalens," *Adv. Mater.*, vol. 29, no. 17, May 2017, Art. no. 1606422.

- [30] F. Liu, O. Tsilipakos, A. Pitilakis, A. C. Tasolamprou, M. S. Mirmoosa, N. V. Kantartzis, D.-H. Kwon, M. Kafesaki, C. M. Soukoulis, and S. A. Tretyakov, "Intelligent metasurfaces with continuously tunable local surface impedance for multiple reconfigurable functions," *Phys. Rev. A*, *Gen. Phys. Appl.*, vol. 11, no. 4, Apr. 2019, Art. no. 044024.

- [31] T. Saeed, C. Skitsas, D. Kouzapas, M. Lestas, V. Soteriou, A. Philippou, S. Abadal, C. Liaskos, L. Petrou, J. Georgiou, and A. Pitsillides, "Fault adaptive routing in metasurface controller networks," in *Proc. 11th Int. Workshop Netw. Chip Archit. (NoCArc)*, Oct. 2018, pp. 1–6.

- [32] A. Pitilakis, A. C. Tasolamprou, C. Liaskos, F. Liu, O. Tsilipakos, X. Wang, M. S. Mirmoosa, K. Kossifos, J. Georgiou, A. Pitsilides, N. V. Kantartzis, S. Ioannidis, E. N. Economou, M. Kafesaki, S. A. Tretyakov, and C. M. Soukoulis, "Software-defined metasurface paradigm: Concept, challenges, prospects," in *Proc. 12th Int. Congr. Artif. Mater. Novel Wave Phenomena (Metamater.)*, Aug. 2018, pp. 483–485.

- [33] A. Pitilakis, "A multi-functional intelligent metasurface?: Electromagnetic design accounting for fabrication aspects," pp. 1–15, 2020, arXiv:2003.08654. [Online]. Available: https://arxiv.org/abs/2003.08654

- [34] L. Petrou, P. Karousios, and J. Georgiou, "Asynchronous circuits as an enabler of scalable and programmable metasurfaces," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2018, pp. 1–5.

- [35] K. B. Unchwaniwala and M. F. Caggiano, "Electrical analysis of IC packaging with emphasis on different ball grid array packages," in *Proc.* 51st Electron. Compon. Technol. Conf., 2001, pp. 1496–1501.

- [36] J. Hasch, E. Topak, R. Schnabel, T. Zwick, R. Weigel, and C. Waldschmidt, "Millimeter-wave technology for automotive radar sensors in the 77 GHz frequency band," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 3, pp. 845–860, Mar. 2012.

- [37] J. Victory, Z. Yan, G. Gildenblat, C. McAndrew, and J. Zheng, "A physically based, scalable MOS varactor model and extraction methodology for RF applications," *IEEE Trans. Electron Devices*, vol. 52, no. 7, pp. 1343–1353, Jul. 2005.

**KYPROS M. KOSSIFOS** (Member, IEEE) was born in Larnaca, Cyprus. He received the Diploma degree in electronic engineering from the TEI of Athens, Athens, Greece, in 2010, and the M.Sc. degree in electrical engineering from the University of Cyprus, Nicosia, Cyprus, in 2015, where he is currently pursuing the Ph.D. degree.

In 2017, he began working on the FETOPEN Project VISORSURF (a Hardware Platform for Software-Driven Functional Metasurfaces). His

research interests include metamaterials, RF/microwave circuits, and antennas.

**LOUKAS PETROU** received the bachelor's degree in electrical engineering from the University of Cyprus, in 2016, and the master's degree in analogue and digital integrated circuit design from the Imperial College London. He is currently pursuing the Ph.D. degree in electrical engineering with the University of Cyprus. His research interests include integrated circuit design and asynchronous digital circuits.

**GIORGOS VARNAVA** received the degree in electrical and computer engineering from the National Technical University of Athens (NTUA), in 2016, with specialization in electronics and systems. He is currently pursuing the Ph.D. degree with the Department of Electrical and Computer Engineering Department, University of Cyprus. His research interests are integrated circuit design, PCB design, and biomedical application for the screening of GI tract by capsule fluorometry.

# IEEE Access

**ALEXANDROS PITILAKIS** received the Diploma degree in electrical engineering from the Department of Electrical and Computer Engineering, Aristotle University of Thessaloniki (AUTh), Greece, in 2005, the M.Sc. degree in electrical engineering from ENST (Telecom), Paris, 2007, and the Ph.D. degree from the Department of Electrical and Computer Engineering, AUTh, in 2013. He holds the position an internship at the Alcatel-Lucent Optical Transmission Systems

Group, Marcoussis, France. He is currently a Postdoctoral Researcher with AUTh, affiliated with the Foundation for Research and Technology Hellas (FORTH), and teaches undergraduate optics, photonics, and antennas and propagation courses in the University of Western Macedonia. His research interests include computational electromagnetics, waveguides and antennas (optical, THz, RF), metamaterials, nonlinear optics, integrated photonics, plasmonics, and graphene. He is a member of OSA.

ANNA C. TASOLAMPROU received the Diploma and Ph.D. degrees in electrical and computer engineering from the Aristotle University of Thessaloniki (AUTh), Greece. She is currently working at the Photonic-Phononic and Meta-Materials (PPM) Group, Institute of Electronic structure and Laser (IESL), Foundation for Research and Technology Hellas (FORTH). Her interests lie in the area of electromagnetics with a focus on the wave propagation properties through

random and periodic media, such as photonic crystals, liquid crystals, 2-D materials, metamaterials, and metasurfaces. She has a long experience in analytical and numerical methods for electrodynamics and an active presence in contemporary applied physics.

**ODYSSEAS TSILIPAKOS** (Senior Member, IEEE) received the Diploma and Ph.D. degrees from the Department of Electrical and Computer Engineering, Aristotle University of Thessaloniki (AUTh), in 2008 and 2013, respectively. From 2014 to 2015, he was a Postdoctoral Research Fellow with AUTh. Since 2016, he has been a Postdoctoral Researcher with the Institute of Electronic Structure and Laser (IESL), Foundation for Research and Technology Hellas (FORTH). His

research interests span metasurfaces and metamaterials, plasmonics and nanophotonics, nonlinear optics in resonant and waveguiding structures, graphene and 2-D photonic materials, and theoretical and computational electromagnetics. He is a member of The Optical Society (OSA).

**MANUEL SECKEL** received the Diploma degree in medical engineering with the University of Applied Sciences of Berlin, in 2008.

In 2008, he joined the Centre of Microperipheric Technologies, Technical University of Berlin. His major research focus is on stretchable substrates process development, reliability, designs for encapsulation and conductor geometries. Other working areas are system design, embedding technologies, and mechanical modeling. He has

recently worked on different EU Projects, such as STELLA, Place.it, PASTA, TERASEL, and MediLight.

**FU LIU** received the B.Sc. degree in applied physics from the China University of Mining and Technology, Xuzhou, China, in 2008, the M.Sc. degree in theoretical physics from Beijing Normal University, Beijing, China, in 2011, and the Ph.D. degree in physics from the City University of Hong Kong, Hong Kong, in 2015. From 2014 to 2016, he was a Research Fellow with the School of Physics and Astronomy, University of Birmingham, Birmingham, U.K. Since 2017,

he has been a Postdoctoral Researcher with the Department of Electronics and Nanoengineering, School of Electrical Engineering, Aalto University, Espoo, Finland.

**DIONYSIOS MANESSIS** received the M.Sc. and Ph.D. degrees in materials science and engineering from the Stevens Institute of Technology, NJ, USA. He received the Project Leadership Certificate from Cornell University, NY, USA. He has worked as a Technologist at Universal Instruments Corporation, NY, USA. Since 2001, he has been a Senior Technology Scientist with Fraunhofer IZM, Berlin. His main research interests lie on fine-pitch flip-chip and wafer-level CSP bumping, solder

balling, materials selection for advanced packaging technologies, embedding processes for heterogeneous integration of components in PCBs and optical PCBs, large scale prototype manufacturing. In the above technical fields, he has published extensively in international conferences and peer-reviewed journals.

**PETROS KAROUSIOS** received the bachelor's degree in electrical engineering from the University of Cyprus, in 2017. He is currently a part-time M.Sc. Student with the Department of Electrical and Computer Engineering, University of Cyprus. He is also employed as a Biomedical Service Engineer. His research interests include integrated circuit design, asynchronous digital circuits, and PCB design.

**NIKOLAOS V. KANTARTZIS** (Senior Member, IEEE) received the Diploma and Ph.D. degrees from the Aristotle University of Thessaloniki (AUTh), Greece, in 1994 and 1999, respectively. He is currently a Professor of computational electromagnetics and electromagnetic compatibility with the School of Electrical and Computer Engineering, AUTh. He has authored/coauthored 3 books, 9 book chapters, and more than 135 peer-reviewed journal articles 230 conference papers.

His primary research interests include computational electromagnetics, metamaterials, graphene, real-world EMC/EMI problems, microwaves and antennas, and nanotechnology devices. He is a member of ICS and ACES.

**DO-HOON KWON** (Senior Member, IEEE) received the B.S. degree in electrical engineering from the Korea Advanced Institute of Science and Technology, Daejeon, South Korea, in 1994, and the M.S. and Ph.D. degrees in electrical engineering from The Ohio State University, Columbus, OH, USA, in 1995 and 2000, respectively. He was a Senior Engineer with Samsung Electronics Co., Ltd., South Korea, from 2000 to 2006. From 2006 to 2008, he was a Postdoctoral Researcher

with the Material Research Science and Engineering Center, Department of Electrical Engineering, Pennsylvania State University, University Park, PA, USA. In 2008, he joined the Department of Electrical and Computer Engineering, University of Massachusetts at Amherst, Amherst, MA, USA. He was a Summer Faculty Fellow with the Air Force Research Laboratory Sensors Directorate and Wright-Patterson AFB, OH, USA, in 2011. His current research interests include antenna scattering theory, small/wideband antennas and array elements, frequency selective surfaces, metamaterials, cloaking, and transformation electromagnetic/optical device designs. He was a recipient of the inaugural IEEE Antennas and Propagation Society Edward E. Altshuler Prize Paper Award, in 2011.

**MARCO A. ANTONIADES** (Senior Member, IEEE) received the B.A.Sc. degree in electrical engineering from the University of Waterloo, ON, Canada, in 2001, and the M.A.Sc. and Ph.D. degrees in electrical engineering from the University of Toronto, ON, Canada, in 2003 and 2009, respectively.

His research interests include engineered electromagnetic materials (metamaterials, metasurfaces), electrically small antennas, adaptive and

reconfigurable antennas, RF/microwave circuits and devices, implantable/ wearable antennas, microwave imaging, wireless power transfer, and radio-frequency identification.

Dr. Antoniades is a member of the IEEE AP-S Education Committee. He was a recipient of the Hellenic Canadian Federation of Ontario Academic Excellence Award, in 2003, the First Prize in the Student Paper Competition at the 2006 IEEE AP-S International Symposium on Antennas and Propagation (AP-S/URSI), the Best of IEEE Computer Architecture Letters Award, in 2018, and the Teaching Innovation Award from the University of Cyprus, in 2018. He has served as an Associate Editor for *IET Microwaves, Antennas & Propagation*, from 2014 to 2018, the Conference Chair of the 2015 Loughborough Antennas and Propagation Conference (LAPC), and on the Steering Committee for the 2010 IEEE AP-S/URSI International Symposium. He serves as the Co-Chair of the Technical Program Committee for the 2020 AP-S/URSI International Symposium. He is also an Associate Editor of the IEEE TRANSACTIONS ON ANTENNAS AND PROPAGATION and the IEEE ANTENNAS AND WIRELESS PROPAGATION LETTERS.

**JULIUS GEORGIOU** (Senior Member, IEEE) received the M.Eng. degree in electrical and electronic engineering and the Ph.D. degree from the Imperial College London, in 1998 and 2003, respectively.

For two years, he worked as the Head of Micropower Design in a technology start-up company, Toumaz Technology. In 2004, he joined Johns Hopkins University as a Postdoctoral Fellow, before becoming a Faculty Member at the Univer-

sity of Cyprus, from 2005 onwards. He is currently an Associate Professor with the University of Cyprus. He was a member of the IEEE Circuits and Systems Society Analog Signal Processing Technical Committee. He is a member of the IEEE Circuits and Systems Society. He was a recipient of the Best Paper Award at the IEEE ISCAS 2011 International Symposium and the IEEE BioDevices 2008 Conference. In 2016, he received the 2015 ONE Award from the President of the Republic of Cyprus for his research accomplishments. He was the Chair of the IEEE Biomedical and Life Science Circuits and Systems (BioCAS) Technical Committee. He has served as the General Chair of the 2010 IEEE Biomedical Circuits and Systems Conference and the Action Chair of the EU COST Action ICT-1401 on Memristors-Devices, Models, Circuits, Systems and Applications (MemoCIS). He was an IEEE Circuits and Systems Society Distinguished Lecturer, from 2016 to 2017. He is an Associate Editor of the IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS and *Frontiers in Neuromorphic Engineering* Journal.