This is an electronic reprint of the original article.

This reprint may differ from the original in pagination and typographic detail.

Tiwary, Nikhilendu; Ross, Glenn; Vuorinen, Vesa; Paulasto-Kröckel, Mervi

# Impact of Inherent Design Limitations for Cu–Sn SLID Microbumps on Its Electromigration Reliability for 3D ICs

Published in:

IEEE Transactions on Electron Devices

DOI

10.1109/TED.2022.3224892

Published: 01/01/2023

Document Version

Publisher's PDF, also known as Version of record

Published under the following license:

CC BY

Please cite the original version:

Tiwary, N., Ross, G., Vuorinen, V., & Paulasto-Kröckel, M. (2023). Impact of Inherent Design Limitations for Cu–Sn SLID Microbumps on Its Electromigration Reliability for 3D ICs. *IEEE Transactions on Electron Devices*, 70(1), 222-229. Article 9969996. https://doi.org/10.1109/TED.2022.3224892

This material is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

IEEE TRANSACTIONS ON ELECTRON DEVICES

# Impact of Inherent Design Limitations for Cu–Sn SLID Microbumps on Its Electromigration Reliability for 3D ICs

Nikhilendu Tiwary<sup>®</sup>, *Member, IEEE*, Glenn Ross<sup>®</sup>, *Member, IEEE*, Vesa Vuorinen<sup>®</sup>, and Mervi Paulasto-Kröckel<sup>®</sup>, *Member, IEEE*

Abstract—Continuous scaling of package architectures requires small volume and high-density microbumps in 3D stacking, which often result in solders fully transforming to intermetallic compounds (IMCs). Cu-Sn solid-liquid interdiffusion (SLID) bonding is an attractive technology where the  $\mu$ bumps are fully composed of IMCs. In this work, test structures made up of Cu<sub>3</sub>Sn IMC  $\mu$ bump with a lateral dimension of 25  $\mu$ m imes 25  $\mu$ m and 50  $\mu$ m imes 50  $\mu$ m, respectively, were manufactured on a pair of 4-inch Si wafers demonstrating wafer-level bonding capability. Electromigration (EM) tests were performed for accelerated conditions at a temperature of 150 °C for various current densities ranging from  $\approx$ 2  $\times$  10<sup>4</sup> to 1  $\times$  10<sup>5</sup> A/cm<sup>2</sup>. Scanning electron microscopy (SEM) and elemental dispersive spectroscopy (EDS) were employed to characterize the as-fabricated test structures. Due to Sn squeeze out, Cu<sub>3</sub>Sn was formed at undesired location at the upper Cu trace. Both nondestructive [lock-in thermography (LiT)] and destructive techniques were employed to analyze the failure locations after EM tests. It was observed that the likelihood of failure spots is the current crowding zone along the interconnects in 3D architectures, which gets aggravated due to the formation of Cu<sub>3</sub>Sn in undesirable locations. Thermal runaway was observed even in Cu<sub>3</sub>Sn, which has been shown to be EM-resistant in the past, thus underlining inherent design issues of  $\mu$ bumps utilizing SLID technology.

Index Terms—3D ICs, Cu–Sn solid–liquid interdiffusion (SLID) bonding, electromigration (EM), failure analysis, heterogeneous integration.

Manuscript received 15 September 2022; revised 28 October 2022; accepted 21 November 2022. This work was supported in part by the Power2Power, which is a European co-funded innovation project on Semiconductor Industry, and receives grants in part from the European H2020 Research and Innovation Program, in part by the Electronic Components and Systems for European Leadership (ECSEL) Joint Undertaking, in part by the National Funding Authorities from eight involved countries (the participating countries are Austria, Finland, Germany including the Feee States of Saxony and Thuringia, Hungary, The Netherlands, Slovakia, Spain, and Switzerland) under Grant Agreement no. 826417, and in part by the Innovation Funding Agency Business Finland (formerly Tekes). The review of this article was arranged by Editor P. Thadesar. (Corresponding author: Nikhilendu Tiwary.)

The authors are with the Department of Electrical Engineering and Automation, Aalto University, Otaniemi, FI-00076 Espoo, Finland (e-mail: nikhilendu.tiwary@aalto.fi; glenn.ross@aalto.fi; vesa.vuorinen@aalto.fi; mervi.paulasto@aalto.fi).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2022.3224892.

Digital Object Identifier 10.1109/TED.2022.3224892

#### I. INTRODUCTION

HE 3D stacking of discrete chips with different functionalities is a key requirement for advanced packaging solutions for realization of smart systems, high-performance computing systems, internet of things (IoT), or "More than Moore" technologies [1], [2]. Often, the requirement is on high density, fine pitch, and small-volume interconnects for power efficient, high bandwidth, low latency, and low system cost for 3D heterogeneous packaging technologies [2]. This brings stringent reliability requirements on the interconnects. One of the main failure mechanisms of ultra-fine interconnects is electromigration (EM), which occurs due to momentum transfer from moving electrons to the metallic atoms under the influence of an applied electric field [1], [3]. Moreover, due to the inherent complexities in 3D architectures, such as current crowding at turns, the combined effect of Joule heating and EM has been identified as a dominant failure mechanism in 3D ICs [3].

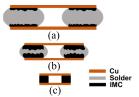

Small-volume interconnections (diameter  $< 100 \mu m$ ) mostly rely on flip chip (FC) bumping technology also known as the "workhorse for advanced packaging solutions" [1]. The FC bumps incorporates a solder layer, such as SnAgCu (SAC) alloys placed in between metallic contacts, Fig. 1(a). With continuous shrinking of the solder volume for high density and fine pitch interconnects, a large volume of solder  $\mu$ bumps gets transformed into intermetallic compounds (IMCs), Fig. 1(b) [4]. These IMCs (hard, high Young's modulus) then not only dominate the mechanical properties of the solders (soft, low Young's modulus), but also degrade their EM reliability performance by offering additional flux divergence paths within the  $\mu$ bump at the solder/IMC interface [5]. The flux divergence in a layer occurs due to different mass diffusivities across layers with different material properties and are the sites of EM failure at high current densities. In contrast, in solid-liquid interdiffusion (SLID) bonding technology, the interconnect formation depends on complete formation of IMCs, Fig. 1(c). These IMCs are metallic interconnects owing to its low resistivity. Moreover, it has been shown that full IMC μbumps offer better EM resistance compared with the solder  $\mu$ bumps [4], [6]. The critical product, which is a measure of the resistance to EM, is reported to be larger for IMC-based  $\mu$ bumps than for soft Sn-based solders [7].

Fig. 1. Schematic of (a) FC bumps with diameter  $D\approx$  100  $\mu$ m and (b) with  $D\approx$  30  $\mu$ m, and (c) SLID bumps with D< 30  $\mu$ m.

Although SLID utilizing various metal combinations has been demonstrated, such as Au-Sn, Ag-Sn, Cu-In, Cu-Sn, and Ni-Sn-Cu, the extensively researched is the Cu-Sn SLID system [8], due to its low cost, simple processing steps, and easy integration with Cu through silicon vias (TSVs) in the system. Here, the Sn layer is equivalent to the solder layer in FC bumps, sandwiched between Cu layers. In the Cu-Sn SLID bonding process, the low melting point (MP)  $T_L$  metal (Sn) is deposited on the higher MP  $T_H$  metal (Cu). The bonding occurs at temperature  $\approx 300$  °C), which is greater than  $T_L$ . As a result, Sn melts with subsequent Cu dissolution and formation of IMCs. At the typical bonding temperature of  $\approx$ 300 °C, the IMCs that could form are Cu<sub>6</sub>Sn<sub>5</sub> (MP—415 °C) and Cu<sub>3</sub>Sn (MP—676 °C) [8]. The Cu<sub>3</sub>Sn IMC is the thermodynamically stable phase, which forms entirely in the bond after which no more Cu is consumed. Since reduction in size of FC  $\mu$ bumps (diameter <30  $\mu$ m) would often result in complete formation of IMCs in  $\mu$ bumps, it will ultimately resemble SLID  $\mu$ bumps, Fig. 1(c) [4]. Therefore, EM studies should be carried out on SLID IMC-based  $\mu$ bumps to examine the failures not only at lower current densities but also catastrophic failures at higher current densities to gain insights to avoid such failures in the real devices.

Limited studies are present in the literature on the EM reliability of fully Cu<sub>3</sub>Sn IMC μbumps. A 20-nm Cu<sub>3</sub>Sn IMC layer on Cu interconnect has been shown to block surface diffusion paths in Cu, thereby enhancing its EM reliability [9]. Moreover, a larger driving force is required to dissociate Cu or Sn atoms from Cu<sub>3</sub>Sn intermetallic layer [9]. Labie et al. [10] demonstrated that fully formed IMC  $\mu$ bumps outperform standard solder bumps in reliability. In other work, Labie et al. [6] compared the EM reliability of two Cu/Sn/Cu samples manufactured with 3.5- and 8-\mu m thickness of Sn. The IMCs present were both Cu<sub>6</sub>Sn<sub>5</sub> (at the middle of the µbump) sandwiched between Cu<sub>3</sub>Sn, which then were connected to Cu under bump metallization (UBM). At the stringent test conditions of  $1.1 \times 10^5$  A/cm<sup>2</sup> at 200 °C, the sample with 8- $\mu$ m Sn layer survived the tests for initial 200 h, whereas the other one (3.5  $\mu$ m of Sn) survived for more than 1000 h with no failures reported [6]. The failure in thick Sn samples was not attributed to the EM-induced damage, but Kirkendall void formation at the Cu/Cu<sub>3</sub>Sn interface when Cu UBM is fully consumed. Chen et al. [4] performed EM tests at a current density of  $2.1 \times 10^5$  A/cm<sup>2</sup> under 180 °C on a full IMC microjoint, and no EM-induced damage was observed for 5000 h of stressing. A negligible resistance increase (4%) after EM test in one of the samples was attributed to the

damage in Al trace connecting the  $\mu$ bumps. Wang et al. [11] performed EM tests at 150 °C on Cu-Cu<sub>3</sub>Sn-Cu microbumps manufactured with a solid-state-diffusion bonding process. For a current density of  $5 \times 10^4$  A/cm<sup>2</sup>, the resistance of the bumps was stable up to 140 h, but it showed an increase in the resistance value when the current density was increased to  $1 \times 10^5$  A/cm<sup>2</sup>. The resistance increase was attributed to the migration of copper layer, but it was not clarified how that increases the resistance. In other work, IMC bumps were EM tested at a current density of  $4 \times 10^5$  A/cm<sup>2</sup> at 200 °C, and a resistance increase of 20% was measured within 1000 h of stressing time [7]. However, the morphology of the IMC contact remained stable, and the failure was related to the formation of Cu-Al IMCs at the lower Al level. In all the above studies, EM resistance capability of IMC μbumps was demonstrated to exceed in comparison with the solder  $\mu$ bumps. Also, the failures in the IMC  $\mu$ bumps were attributed to different mechanisms with mostly damage in the metallization contact layers, which are the current crowding locations [4], [6], [7].

Current crowding locations in 3D ICs have shown to be a major failure spot where thermal runaway problems typically arise as a combined effect of Joule heating and EM [3]. Thermal runaway resulting in local melting at current crowding locations has been reported earlier for eutectic PbSn-based solder [12]. In this work, test structures were fabricated by demonstrating wafer-level SLID bonding to study the reliability of Cu<sub>3</sub>Sn IMCs with Cu at both top and bottom layers. The EM tests were conducted for various current densities at a temperature of 150 °C. Due to the combined effect of Joule heating and EM, thermal runaway was observed even in Cu<sub>3</sub>Sn with a high MP of 676 °C, which was formed at upper Cu trace because of squeeze out and subsequent reaction of Sn during bonding. This work would examine this new failure mechanism not reported before in Cu<sub>3</sub>Sn, which is formed at such undesired locations due to Sn squeeze out and which could easily aggravate in small-volume, fine-pitch SLID μbumps. This emphasizes the inherent limitations in SLID technology and the related design considerations for which the risk is rather underestimated.

### II. EXPERIMENTAL METHODS

# A. Design of Test Structures

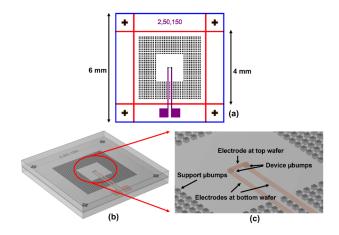

Various test structures, such as two bumps, daisy chain, and kelvin structures, were incorporated in the 4-in mask process. The  $\mu$ bumps were designed to be square in shape with the lateral dimensions ranging from 10 to 100  $\mu$ m. A two-bump test structure was employed for this study. The advantage of this test structure is that the current flow from both top to bottom chip and bottom to top chip could be investigated with focus on just two  $\mu$ bumps. Fig. 2(a) shows the mask layout of the two-bump test structure along with the dimensions of the top and bottom chips. The bottom chip dimensions were 6 mm  $\times$  6 mm, and the top chip dimensions were 4 mm  $\times$  4 mm. The scribe lines used to dice the bonded chips are shown in red (partial cut) and blue (through cut).

Fig. 2. (a) Layout of the chip with a two-bump test structure. Violet traces are the contacts on the bottom wafer, and green traces are the contacts on the top wafer. Bottom and top wafers are bonded through the bumps (black), (b) 3D schematic of the bonded chip, and (c) zoomed-in 3D schematic of the two-bump test structure.

The partial cuts denote the locations where only the top chip was diced to expose the Cu contact pads on the bottom chip for probing. The through cut denotes the locations where both top and bottom chips were diced. An array of support  $\mu$ bumps were also provided to mitigate the stress formed during the dicing process. Fig. 2(b) and (c) shows the 3D schematic of the bonded chip highlighting the device  $\mu$ bumps, support  $\mu$ bumps, and top and bottom Cu traces. In this work, the two-bump test structures, which were investigated, were of two lateral dimensions, i.e., 25 and 50  $\mu$ m.

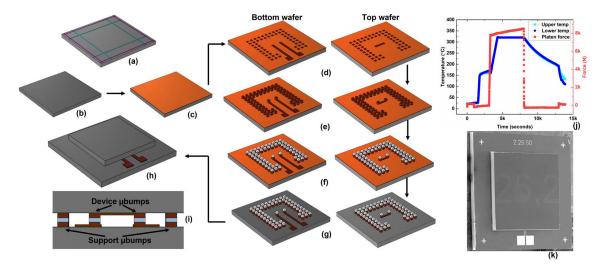

#### B. Device Fabrication

The fabrication of the test structures is a four-mask process. It starts with a pair of 4-inch double-sided polished (DSP) 100-orientated Si wafer. In the first step, the back-side patterning was carried out on the wafer pair, wherein the alignment marks and scribe lines were patterned using optical lithography and etched with reactive ion etching (RIE) tool with SF<sub>6</sub> as an etching gas for both bottom and top wafers, Fig. 3(a). A 15 nm of titanium tungsten (TiW) adhesion layer and a 100 nm of Cu seed layer were then sputter deposited on the front side of both the wafer pairs, Fig. 3(b) and (c). The front side of the wafer pair was then patterned to form the traces, contact pads, and support  $\mu$ bumps using an AZ15nXT (450 CPS) negative photoresist. The patterned wafer pair was treated with an oxygen plasma with an O<sub>2</sub> flowrate of 30 mL/min and an RF power of 100 W for 3 min to improve the wettability of the surface before electroplating. A 1  $\mu$ m of Cu was then electroplated at a current density of 15 mA/cm<sup>2</sup> with NB SEMIPLATE CU 100 after which the resist was stripped, Fig. 3(d). Then, the device  $\mu$ bumps and the support  $\mu$ bumps were subsequently patterned using the same photoresist and treated with the oxygen plasma as described before. Subsequently, 4 µm of Cu (NB SEMIPLATE CU 100) and 2.5 μm of Sn (NB SEMIPLATE SN 100) were electroplated at a current density of 15 and 10 mA/cm<sup>2</sup>, respectively, Fig. 3(e) and (f). After every electroplating step, the thickness was confirmed by a contact profilometer at five different locations

across wafer. The final thickness of electrodeposited Cu and Sn was measured to be Cu—5.1  $\pm$  0.3  $\mu$ m and Sn—2.3  $\pm$  0.2  $\mu$ m for bottom wafer and Cu—4.9  $\pm$  0.2  $\mu$ m and Sn—2.5  $\pm$  0.3  $\mu$ m for top wafer.

After stripping the resist, the final patterning was done with the photoresist to protect the Cu traces and device μbumps during the etching step of the Cu seed layer and TiW adhesion layer. Cu was etched in a commercial etchant Cu etch 150 purchased from NB technologies GmbH, and TiW was etched in an H<sub>2</sub>O<sub>2</sub> solution heated at 60 °C, Fig. 3(g). The etching of Cu and TiW layers was visually confirmed under an optical microscope before stripping the resist. Finally, the wafer bonding process was carried out in an Applied Microengineering Limited (AML) wafer bonder. The wafers were mounted on the top and bottom platens, and the chamber was pumped down to  $\approx 1e - 6$  bar. The wafers were preheated to 150 °C before bringing them into contact. After alignment of the wafers, a force of 8 kN  $\approx$ 20 MPa, total bonding area— 4 cm<sup>2</sup>) was applied on the platens, and the temperature was ramped up to 320 °C at a ramp up rate of 10 °C/min. The bonding was then carried out for 1-h duration, after which the temperature was ramped down. Finally, the bonded wafer pairs were diced along the through and partial cut scribe lines on a DAD3220 dicer tool from Disco, Fig. 3(h). Fig. 3(i) shows the schematic of the bond line, Cu-Cu<sub>3</sub>Sn-Cu. Fig. 3(j) shows the platen force and temperatures versus time from the wafer bonding process. A good match was there between the temperatures of the upper and lower platens. Fig. 3(k) shows the scanning electron microscopy (SEM) image of the final fabricated chip.

# C. Nondestructive Analysis

The nondestructive analysis of the chips was carried out with two techniques. Phoenix GE Nanomex with minimum detectability of 200 nm was employed for X-ray imaging of the chips. Sentris from Optotherm Inc. was employed for lockin thermography (LiT) to locate the failure zones in the EM stressed chips.

### D. Destructive Analysis

As can be seen from Fig. 2, the device bumps are at the middle of the chip. To assess it for cross-sectional imaging, the chips were first cut in two parts along a horizontal cutline at the vicinity of the device  $\mu$ bumps ( $\approx$ 300  $\mu$ m away) with a femtosecond laser micromachining tool. A femtosecond laser has now been widely used for destructive analysis, which generates negligible laser-induced damage to the samples [13]. The cut chips were then molded into epoxy and cured for subsequent grinding and polishing steps, which was carried out using standard metallographic methods.

# E. SEM Characterization

After sample preparation, the initial cross-sectional imaging of the support bumps and elemental dispersive spectroscopy (EDS) point analysis was carried out with JEOL JSM-6335F field-emission SEM (FESEM) equipped with the Oxford Instruments INCA X-sight EDS detector. After EM tests,

Fig. 3. (a) Back side patterning for scribe lines, magenta for bottom wafer (through cut), and cyan for top wafer (partial cut—only top wafer), (b) front side Si wafer, (c) TiW/Cu deposition, (d) patterning and electrodeposition of Cu electrodes on bottom and top wafers, (e) patterning and electrodeposition of Cu bumps, (f) electrodeposition of Sn bumps, (g) etching of Cu seed layer and TiW, (h) wafer bonding and dicing, (i) cut plane across the chip showing the Cu (brown)—Cu<sub>3</sub>Sn (blue)—Cu (brown) bond line, (j) wafer bonding process profile, and (k) SEM image of the as-fabricated chip.

the cross-sectional imaging and in-depth analysis of the test structures were carried out with a dual beam focused ion beam (FIB)-SEM JEOL JIB-4700F equipped with the Oxford instruments Ultim Max 100 EDS detector.

## F. EM Tests

Before the EM tests, a current-voltage (I-V) sweep analysis was performed on the as-fabricated chips to assess the linear resistance of the bumps. The I-V tests were conducted via an Agilent B1500 semiconductor parameter analyzer. A voltage sweep from -0.5 to 0.5 V was performed, and the corresponding current values were recorded. Subsequently, EM tests were performed on a thermal chuck at 150 °C with Keithley 2231A-30-3 three-channel dc power supply with nominal current densities across the  $\mu$ bumps ranging from  $2 \times 10^4$  to  $1 \times 10^5$  A/cm<sup>2</sup>. The current densities were calculated based on the ideal dimensions of  $\mu$ bumps (25 and 50  $\mu$ m<sup>2</sup>).

#### III. RESULTS AND DISCUSSION

#### A. SEM Cross-Sectional Imaging

Fig. 4(a) and (b) shows the cross-sectional SEM images of the support  $\mu$ bumps of 25- and 50- $\mu$ m test structures, respectively. The EDS point analysis of the  $\mu$ bumps shows that Cu<sub>3</sub>Sn was formed in the bond line, with the atomic percentage of Cu and Sn as  $\approx 73.8\% \pm 0.3\%$  and  $\approx 26.2\% \pm 0.3\%$ , respectively. Moreover, in the support  $\mu$ bumps from 50- $\mu$ m test structures, small amount of Cu<sub>6</sub>Sn<sub>5</sub> was observed, Fig. 4(b). It was also confirmed with the EDS point analysis with the atomic percentage of Cu and Sn as  $\approx 58.0\% \pm 1.8\%$  and  $\approx 42.0\% \pm 1.8\%$ , respectively. However, Cu<sub>6</sub>Sn<sub>5</sub> was not observed in the support  $\mu$ bumps from 25- $\mu$ m test structures.

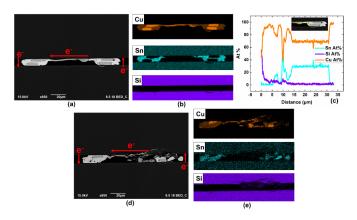

Fig. 4(c) and (e) shows the SEM images of the device  $\mu$ bumps from 25- and 50- $\mu$ m test structures, respectively.

Cu<sub>3</sub>Sn was also observed to be formed on the top Cu trace, which is due to the squeeze out of liquid Sn during the bonding process [shown in Fig. 4(c) (red circle)]. Ideally, the upper Cu trace should connect the Cu pads of the two µbumps, as shown in the schematic of Fig. 3(i). Fig. 4(d) and (f) shows the EDS elemental mapping of Cu, Sn, and Si on the test structures. Fig. 4(g) and (h) shows the atomic percentage plots across the cutline shown in the inset, respectively. As can be seen, full Cu<sub>3</sub>Sn was formed in the bond line, and the atomic weight percentage of the Cu and Sn was found to be  $\approx 71.1\% \pm 1.8\%$  and  $\approx 27.2\% \pm 1.9\%$ , respectively. No Cu<sub>6</sub>Sn<sub>5</sub> was observed in the device μbumps of the test structures under consideration. The height of all the  $\mu$ bumps measured was  $\approx 11 \ \mu m$ . The total thickness of the electroplated Cu and Sn stack from top and bottom wafer was  $\approx$ 15  $\mu$ m, so the reduction in thickness of the final bond line is attributed to the squeeze out of liquid Sn. Moreover, formation of voids could be seen in the test structures concentrated mostly at the Cu/Cu<sub>3</sub>Sn interface, which is widely reported due to interplay of various parameters, such as Kirkendall voiding and impurities incorporation in the electroplated structures [14], [15].

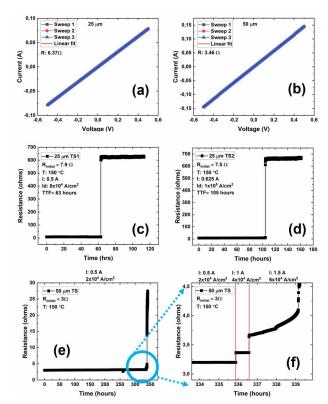

# B. I-V Sweep and EM Tests

Fig. 5(a) and (b) shows the linear I-V characteristics of the two-bump test structures performed before the EM tests. The resistance of the two-bump test structures measured varied from 6 to 7  $\Omega$  and 3 to 4  $\Omega$  for the 25- and 50- $\mu$ m test structure, respectively. Fig. 5(c) shows the EM test of a 25- $\mu$ m test structure (25- $\mu$ m TS1) conducted on a thermal chuck at 150 °C at a current density of  $\approx$ 8 × 10<sup>4</sup> A/cm<sup>2</sup> (current value 0.5 A). The resistance was stable for  $\approx$ 63 h [time to failure (TTF)] after which there was a sudden jump in the resistance value, which was stable for further 30 h. Fig. 5(d) shows the EM test result of another 25- $\mu$ m test structure (25- $\mu$ m TS2)

Fig. 4. (a) SEM image of 25- $\mu$ m support bumps, (b) SEM image of 50- $\mu$ m support bumps, and (c) SEM image of 25- $\mu$ m two-bump test structure. Cu<sub>3</sub>Sn formed due to Sn squeeze out at the upper Cu trace is shown in red circle, (d) EDS elemental maps of the 25- $\mu$ m test structure, (e) SEM image of 50- $\mu$ m two-bump test structure, (f) EDS elemental maps of the 50- $\mu$ m test structure, and atomic percentage plot versus distance across the cutline shown in the inset figure for (g) 25- $\mu$ m device  $\mu$ bump and (h) 50- $\mu$ m device  $\mu$ bump.

conducted at 150 °C and at a current density of  $\approx 1 \times 10^5$  A/cm<sup>2</sup>. In this case, the resistance was stable for  $\approx 105$  h before the failure.

For the 50- $\mu m$  test structure (50- $\mu m$  TS), for the current level of 0.5 A, the current density corresponds to  $\approx 2 \times 10^4$  A/cm². At this current density, the resistance was observed to be stable for  $\approx 336$  h (approximately two weeks), and no failure was recorded, Fig. 5(e) and (f). The current density was then increased to  $\approx 4 \times 10^4$  A/cm² and monitored for  $\approx 40$  min during which the resistance was again stable. The small increase in the base resistance because of increase in current could be attributed to the Joule heating, which increased the measured resistance value. Subsequently, the current density was increased to  $\approx 6 \times 10^4$  A/cm² (current—1.5 A), and the resistance was observed to gradually increase after which the test was terminated.

# C. Failure Analysis

1) Nondestructive Failure Analysis: Two techniques were employed for the nondestructive analysis of the failure spots

Fig. 5. I–V characteristics of (a) 25- $\mu$ m test structure and (b) 50- $\mu$ m test structure, EM tests of 25- $\mu$ m test structures for a current density of (c) 8  $\times$  10<sup>4</sup> and (d) 1  $\times$  10<sup>5</sup> A/cm<sup>2</sup>, and (e) and (f) EM tests of the 50- $\mu$ m test structure.

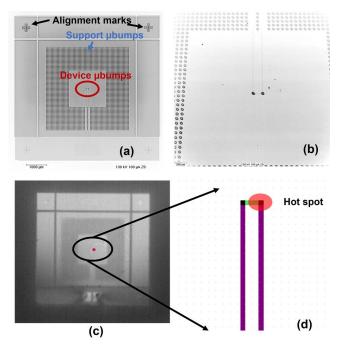

Fig. 6. (a) 2-D X-ray image of  $25-\mu m$  TS1 chip with the device  $\mu$ bumps and support  $\mu$ bumps marked, (b) zoomed-in image of the device bumps with tilt, (c) LiT thermal image of the chip showing the hot spot, which indicates probable failure location, and (d) schematic showing the location of the hot spot in (c).

in the EM tested sample—X-ray imaging and LiT. The X-ray imaging of the chips is an effective way of examining the  $\mu$ bumps and checking the alignment of the chips.

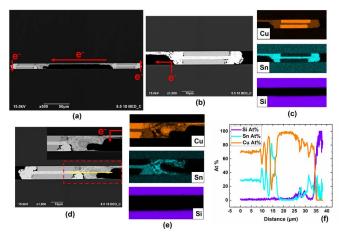

Fig. 7. (a) SEM image of EM tested 25- $\mu$ m TS1 for a current density of  $8 \times 10^4$  A/cm² with the electron current direction shown, (b) corresponding EDS elemental maps, (c) atomic percentage plot versus distance across the cutline shown in the inset, (d) SEM image of EM tested 25- $\mu$ m TS2 for a current density of  $10^5$  A/cm² with the electron current direction shown, and (e) corresponding EDS elemental maps.

Fig. 6(a) shows the image of an entire chip, where device  $\mu$ bumps and support  $\mu$ bumps are marked. The alignment marks at the top corners (left and right) demonstrate good alignment of the top and bottom chips. Fig. 6(b) shows the zoomed-in image of the device  $\mu$ bumps. Two limitations were recognized: 1) small size—the size of the bumps was  $\approx 25 \ \mu\text{m} \times 25 \ \mu\text{m} \times 11 \ \mu\text{m}$ , which is too low for effective analysis and 2) the device  $\mu$ bumps were surrounded by the support  $\mu$ bumps, which makes the full 3D image construction of the device  $\mu$ bumps challenging.

On the other hand, LiT demonstrated effectiveness in locating the failure spots. The applied voltage during the LiT tests was set to 8.5 V at a frequency of 2.5 Hz, and the thermal image was acquired after 46 cycles. Fig. 6(c) shows the infrared (IR) thermal image of EM stressed sample for 25- $\mu$ m test structure (25- $\mu$ m TS1) of which the EM test result is shown in Fig. 5(c). The hot spot corresponding to the probable failure location near the device  $\mu$ bumps is clearly visible.

2) Destructive Failure Analysis (FIB): A destructive analysis was carried out to explore the probable failure locations in detail. Fig. 7(a) and (b) shows the SEM and elemental EDS mapping of the device  $\mu$ bumps from 25- $\mu$ m TS1, which was EM tested [Fig. 5(c)] and on which the LiT analysis was performed [Fig. 6(c)]. Cu traces were found to be delaminated near the location where hot spot was observed. Due to delamination, the dissipation of Joule heating gets affected, which results in hot spot formation adjacent to those locations. On the other hand, accumulation of Cu was observed on the Cu trace near to the right bump, Fig. 7(a). Fig. 7(c) shows the EDS line scan generated from the cutline shown in the inset. With closer analysis of the line scans, diffusion of Sn into the Cu trace due to EM could be suspected. The diffusion of Sn in the direction of electronic current at higher temperatures has also been widely reported in the literature for solder bumps [16].

Fig. 7(d) and (e) shows the SEM and elemental EDS mapping of 25- $\mu$ m TS2 sample, which was tested at a current density of  $\approx 1 \times 10^5$  A/cm<sup>2</sup> [Fig. 5(d)]. As can be seen

Fig. 8. (a) SEM image of EM tested 50- $\mu$ m TS with the electron current direction shown, (b) zoomed-in SEM image of the right bump and (c) corresponding EDS elemental maps, (d) zoomed-in SEM image of the left bump and (e) corresponding EDS elemental maps, and (f) atomic percentage plot versus distance across the yellow cutline shown in (d).

from the elemental maps, complete burnout and melting of  $\mu$ bump and silicon were observed in the right bump. Also, delamination [similar to Fig. 7(a)] and cracking of upper Cu trace were observed near the left bump. However, no detailed information could be extracted regarding the initiation and mechanism of failure, as the tests continued for almost  $\approx$ 55 h after the failure [Fig. 5(d)].

Fig. 8(a) shows the SEM image of the 50-µm TS for which the EM test is shown in Fig. 5(e) and (f). The EM tests were terminated when sudden increase in the resistance was observed at a current density of  $\approx 6 \times 10^4$  A/cm<sup>2</sup>. Fig. 8(b) and (c) shows the zoomed-in SEM image of the right bump and elemental EDS maps, respectively. No failure spots were observed at this location. In contrast to the  $25-\mu m$  test structures [Fig. 7(a) and (d)], the right bump is fully intact. This could be due to the lower current density (even for max— $6 \times 10^4$  A/cm<sup>2</sup>) because of the 4× increase in the cross-sectional area as compared with 25- $\mu$ m test structures. Fig. 8(d) and (e) shows the SEM image and the elemental maps of the left bump, respectively. From the mapping result, a segregation of Cu and Sn could be observed in the Cu<sub>3</sub>Sn layer near the upper Cu trace, which indicates local melting, as no thermodynamically stable phase could be identified from Cu-Sn system phase diagram with respect to the measured Cu-Sn atomic percentages. Fig. 8(f) shows the atomic percentage plots versus distance across the yellow cutline shown in Fig. 8(d). At the middle of the bump, the composition indicates Cu<sub>3</sub>Sn but clearly deviates and shows irregular Cu- and Sn-rich regions. Since the region that was originally Cu<sub>3</sub>Sn is supposed to be EM-resistant and thermally stable until 676 °C, observation of these kind of failures has not been reported before.

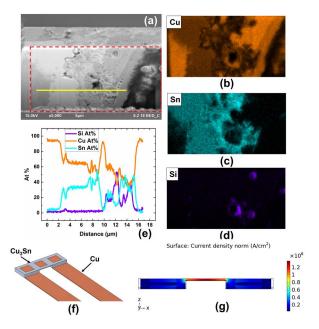

Then, FIB milling was carried out to examine the region underneath the surface of the failure location. Fig. 9(a)–(d) shows the SEM image after FIB cut and the corresponding elemental map data for Cu, Sn, and Si. The Cu- and Sn-rich regions also penetrate beneath the surface. Interestingly, silicon was also found to be incorporated in traces at the

Fig. 9. (a) SEM image after FIB cut of the failure location, elemental maps for (b) Cu, (c) Sn, (d) Si, (e) atomic percentage plots across cutline shown in Fig. 8(a), (f) model schematic of the two-bump test structure, and (g) current density distribution across a cut plane midway of the test structure.

failure location. Fig. 9(e) shows the EDS line scan across the yellow cutline shown in Fig. 9(a), which confirmed the presence of silicon. Although the current density across the 50- $\mu$ m bumps is lower than 25- $\mu$ m bumps (4× cross-sectional area difference), the current density across the upper Cu trace of 50- $\mu$ m test structure is higher than the Cu trace of 25- $\mu$ m test structure (2× cross-sectional area difference) for the maximum current of 1.5 A. Furthermore, even though the EM tests were conducted at 150 °C, the actual temperature near the  $\mu$ bumps at the current crowding zone could be much higher due to Joule heating [3]. As a result, the resistance at the current crowding zone would further increase, ultimately resulting in thermal runaway. This would then result in the local melting of Cu<sub>3</sub>Sn and dissolution of Si in the melt with subsequent solidification after the tests are terminated.

To assess the current density levels, the  $50-\mu m$  two-bump test structure was constructed in the finite element (FE) model in COMSOL by accounting the Cu<sub>3</sub>Sn formation due to Sn squeeze out across the Cu bumps, Fig. 9(f). Here, Cu<sub>3</sub>Sn formation fully encloses the Cu bump to mimic the experimental observation. The electrical conductivities of Cu and Cu<sub>3</sub>Sn were taken as  $58.1 \times 10^6$  and  $11.2 \times 10^6$  S/m, respectively. Fig. 9(g) shows the current density distribution for a current of 1 A across a cut plane from the center of the two-bump test structure. The current density is an order of magnitude higher near to the location where failures were observed as compared with the current density in  $\mu$ bumps. Moreover, the resistivity of Cu<sub>3</sub>Sn is also higher than Cu, which also worsen the scenario due to Joule heating at the current crowding locations resulting in thermal runaway. This shows that Cu<sub>3</sub>Sn though it is thermally stable until 676 °C, such kind of failures could also occur, underlining the importance of proper designing of

the SLID  $\mu$ bumps in 3D ICs. Specifically, care must be taken to minimize Sn squeeze out during the bonding process to ultimately prevent Cu<sub>3</sub>Sn formation in unwanted locations.

#### IV. CONCLUSION

In this work, the wafer-level Cu–Sn SLID bonding process was demonstrated by incorporating various test structures. Due to Sn squeeze out, Cu<sub>3</sub>Sn was observed to form at unwanted locations at the upper Cu trace connecting the two-bump test structure. The test structures were tested for its EM reliability to study different failure modes. For  $25-\mu m$ test structures, two types of failures were observed. For a current density of  $8 \times 10^4$  A/cm<sup>2</sup>, delamination of Cu traces was observed, whereas catastrophic failure in addition to delamination of Cu trace was observed at a higher current density of  $1 \times 10^5$  A/cm<sup>2</sup>. For the 50- $\mu$ m test structure, thermal runaway-based failure was observed in Cu<sub>3</sub>Sn at current crowding location. Therefore, although Cu<sub>3</sub>Sn has been shown to be EM-resistant with high thermal stability, thermal runaway and catastrophic failures could not be ruled out in Cu<sub>3</sub>Sn in 3D architectures at high current densities due to its formation at unwanted locations. This emphasizes the need of proper designing of SLID  $\mu$ bumps in heterogeneous integration to prevent Sn squeeze out and prevent the formation of Cu<sub>3</sub>Sn at undesired locations. This would include proper design considerations to minimize Sn squeeze out, which includes the following: 1) engineering lateral dimensions of the bumps in top and bottom wafers; 2) optimal Sn thickness; and 3) optimal bonding force. The above aspects are easy to control in chip-level bonding, but will be difficult to control in the wafer-level bonding process where nonuniformities in the thickness of electroplating stacks could pose problems on the overall yield. Future work will incorporate these aspects to address the inherent limitations in SLID  $\mu$ bumps for interconnects for enhanced EM reliability.

#### **ACKNOWLEDGMENT**

The authors acknowledge the provision of facilities and technical support at Aalto University OtaNano-Micronova Nanofabrication Centre for samples manufacturing, and Nanomicroscopy center for focused ion beam (FIB)-scanning electron microscopy (SEM) studies. They would also like to thank VTT Technical Research Centre of Finland, Espoo for electromigration (EM) tests, and ABB, Helsinki, Finland, for nondestructive [X-ray and lock-in thermography (LiT)] measurements on the samples.

# REFERENCES

- "IEEE international roadmap for devices and systems," 2020 ed., Packag. Integr. White Paper, 2017, pp. 1–22.

- [2] "IEEE heterogeneous integration roadmap," in *Chapter 1: HIR Overview and Executive Summary*, 2019 ed., 2019, pp. 1–14.

- [3] K. N. Tu, Y. Liu, and M. Li, "Effect of Joule heating and current crowding on electromigration in mobile technology," *Appl. Phys. Rev.*, vol. 4, no. 1, Mar. 2017, Art. no. 011101, doi: 10.1063/1.4974168.

- [4] H.-Y. Chen et al., "Electromigration immortality of purely intermetallic micro-bump for 3D integration," in *Proc. IEEE 65th Electron. Compon. Technol. Conf. (ECTC)*, San Diego, CA, USA, May 2015, pp. 620–625, doi: 10.1109/ECTC.2015.7159656.

- [5] Y.-W. Chang et al., "Electromigration mechanism of failure in flipchip solder joints based on discrete void formation," *Sci. Rep.*, vol. 7, Dec. 2017, Art. no. 17950, doi: 10.1038/s41598-017-06250-8.

- [6] R. Labie, P. Limaye, K. Lee, C. Berry, E. Beyne, and I. De Wolf, "Reliability testing of Cu-Sn intermetallic micro-bump interconnections for 3D-device stacking," in *Proc. 3rd Electron. Syst. Integr. Technol. Conf. (ESTC)*, Berlin, Germany, Sep. 2010, pp. 1–5, doi: 10.1109/ESTC.2010.5642925.

- [7] A. Munding, H. Hubner, A. Kaiser, S. Penka, P. Benkart, and E. Kohn, "Cu/Sn solid-liquid interdiffusion bonding," in *Wafer Level 3-D ICs Process Technology*, C. S. Tan, R. J. Gutmann, and L. R. Reif, Eds. New York, NY, USA: Springer-Verlag, 2008, pp. 131–169, doi: 10.1007/978-0-387-76534-1\_7.

- [8] L. Sun, M.-H. Chen, L. Zhang, P. He, and L.-S. Xie, "Recent progress in SLID bonding in novel 3D-IC technologies," J. Alloys Compounds, vol. 818, Mar. 2020, Art. no. 152825, doi: 10.1016/j.jallcom.2019.152825.

- [9] M. Y. Yan et al., "Effect of Cu<sub>3</sub> Sn coatings on electromigration lifetime improvement of cu dual-damascene interconnects," *Appl. Phys. Lett.*, vol. 87, no. 21, Nov. 2005, Art. no. 211103, doi: 10.1063/1.2132536.

- [10] R. Labie, W. Ruythooren, K. Baert, E. Beyne, and B. Swinnen, "Resistance to electromigration of purely intermetallic micro-bump interconnections for 3D-device stacking," in *Proc. Int. Interconnect Technol. Conf.*, Burlingame, CA, USA, Jun. 2008, pp. 19–21, doi: 10.1109/IITC.2008.4546913.

- [11] J. Wang, Q. Wang, Z. Wu, D. Wang, and J. Cai, "Solid-state-diffusion bonding for wafer-level fine-pitch Cu/Sn/Cu interconnect in 3-D integration," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 7, no. 1, pp. 19–26, Jan. 2017, doi: 10.1109/TCPMT.2016.2626794.

- [12] C. M. Tsai, Y. L. Lin, J. Y. Tsai, Y.-S. Lai, and C. R. Kao, "Local melting induced by electromigration in flip-chip solder joints," *J. Electron. Mater.*, vol. 35, no. 5, pp. 1005–1009, May 2006, doi: 10.1007/BF02692560.

- [13] Y. Li, P. K. M. Srinath, and D. Goyal, "A review of failure analysis methods for advanced 3D microelectronic packages," *J. Electron. Mater.*, vol. 45, no. 1, pp. 116–124, Jan. 2016, doi: 10.1007/s11664-015-4165-y.

- [14] G. Ross, V. Vuorinen, and M. Paulasto-Kröckel, "Void formation and its impact on Cu–Sn intermetallic compound formation," *J. Alloys Compounds*, vol. 677, pp. 127–138, Aug. 2016, doi: 10.1016/j.jallcom.2016.03.193.

- [15] N. Tiwary, V. Vuorinen, G. Ross, and M. Paulasto-Kröckel, "Finite element simulation of solid–liquid interdiffusion bonding process: Understanding process-dependent thermomechanical stress," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 12, no. 5, pp. 847–856, May 2022, doi: 10.1109/TCPMT.2022.3170082.

- [16] T. Laurila, J. Karppinen, V. Vuorinen, A. Paul, and M. Paulasto-Kröckel, "Effect of constant and cyclic current stressing on the evolution of intermetallic compound layers," *J. Electron. Mater.*, vol. 40, no. 7, pp. 1517–1526, Jul. 2011, doi: 10.1007/s11664-011-1632-y.